执行和提取整个指令所需的时间称为指令周期。它包含:

- 提取周期–通过存储在程序计数器(PC)中的地址提取下一条指令,然后将其存储在指令寄存器中。

- 解码指令–解码器解释指令寄存器中的编码指令。

- 读取有效地址–从主存储器中读取指令中给出的地址,并获取所需的数据。有效地址取决于直接寻址模式或间接寻址模式。

- 执行周期–包括存储器读取(MR),存储器写入(MW),输入输出读取(IOR)和输入输出写入(IOW)

微处理器完成访问存储器或输入/输出设备的操作所需的时间称为机器周期。微处理器频率的一个时间周期称为t状态。从一个时钟脉冲的下降沿到下一时钟脉冲的下降沿测量t状态。

提取周期需要四个t状态,执行周期需要三个t状态。

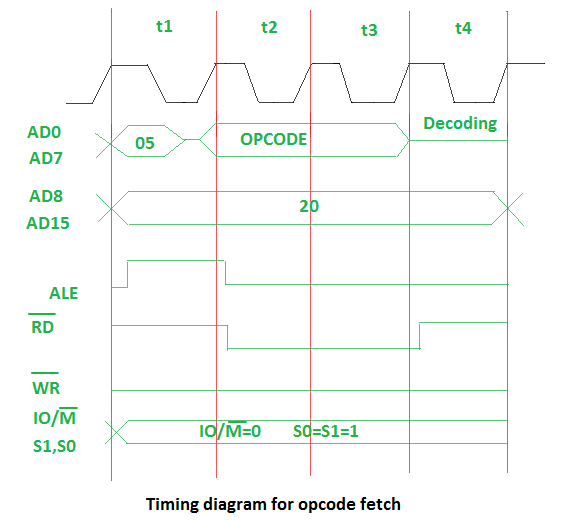

提取周期或操作码提取的时序图:

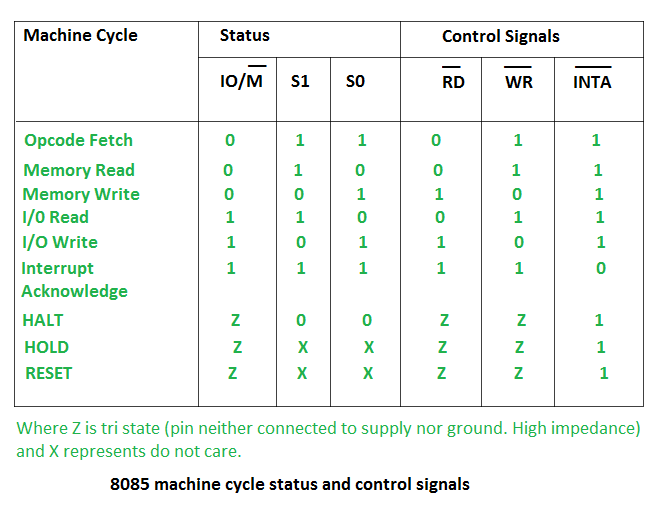

上图表示:

- 05 –存储操作码的地址的低位。使用多路复用地址和数据总线AD0-AD7。

- 20 –存储操作码的地址的高位。使用多路复用地址和数据总线AD8-AD15。

- ALE –为多路复用地址和数据总线提供信号。如果信号为高电平或1,则复用地址和数据总线将用作地址总线。为了获取地址的低位,信号为1,以便多路复用总线可以用作地址总线。如果信号为低电平或0,则将多路复用总线用作数据总线。当获取地址的低位时,由于信号为低电平,因此它将充当数据总线。

- RD(低电平有效)–如果信号为高电平或1,则微处理器不会读取任何数据。如果信号为低电平或0,则微处理器读取数据。

- WR(低有效)–如果信号为高电平或1,则微处理器不会写入任何数据。如果信号为低电平或0,则由微处理器写入数据。

- IO / M(低电平有效)和S1,S0 –如果信号为高电平或1,则正在对输入输出进行操作。如果信号为低电平或0,则正在存储器上执行操作。