- eprom ic (1)

- 数字ic的第一个数字c#(1)

- 数字ic的第一个数字c#代码示例

- eprom ic - 任何代码示例

- ic如何获取div jq的id - Javascript(1)

- ic如何获取div jq的id - Javascript代码示例

- proteus rom ic (1)

- proteus rom ic - 任何代码示例

- IC 市场最低存款 - TypeScript (1)

- IC 市场最低存款 - TypeScript 代码示例

- android application ic_launcher dimmensions - Dart 代码示例

- AAPT:错误:找不到资源可绘制 ic_stat_icone_app_final_2(又名 com.procam.fleeting.br:drawable ic_stat_icone_app_final_2). - Javascript(1)

- AAPT:错误:找不到资源可绘制 ic_stat_icone_app_final_2(又名 com.procam.fleeting.br:drawable ic_stat_icone_app_final_2). - Javascript代码示例

- python代码示例中的索引

- python 跟踪表 - Python 代码示例

- ruby 数组减数组 - Ruby 代码示例

- 素数的递归程序

- Python|提取过滤的字典值

- 两个整数之间的最大互质集

- html 文本框 - Html 代码示例

- Python – GTK+ 3 中的网格容器

- 在 termux 中安装 msf - Shell-Bash 代码示例

- 检查是否可以通过与上一跳重复多次,少跳一次或相同数目的索引重复跳转来到达已排序数组的末尾

- 从0到N的连续数字的汉明差总和|套装2

- Kexilies - 任何代码示例

- nodejs 临时文件 - Javascript 代码示例

- 检查数组的素数元素的和是否为素数

- 如何在python代码示例中打印字符串

- 给定2D数组中的最小和子矩阵

📅 最后修改于: 2020-11-24 07:05:15 🧑 作者: Mango

锁相环(PLL)是线性系统中的重要模块之一。在雷达,卫星,FM等通讯系统中很有用。

本章详细讨论了PLL和IC 565的框图。

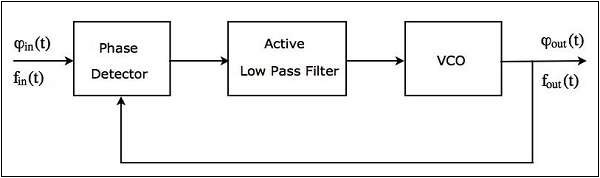

PLL框图

锁相环(PLL)主要由以下三个模块组成–

- 鉴相器

- 有源低通滤波器

- 压控振荡器(VCO)

PLL的框图如下图所示-

相位检测器的输出用作有源低通滤波器的输入。同样,有源低通滤波器的输出用作VCO的输入。

PLL的工作如下-

-

鉴相器产生直流电压,该直流电压与频率为$ f_ {in} $的输入信号与频率为$ f_ {out} $的反馈(输出)信号之间的相位差成比例。

-

鉴相器是一个乘法器,它在输出处产生两个频率分量-频率$ f_ {in} $和$ f_ {out} $以及频率差$ f_ {in} $和$ f_ {out} $的总和。

-

有源低通滤波器在消除了相位检测器输出中存在的高频分量之后,会在其输出端产生直流电压。它还会放大信号。

-

当没有输入时, VCO会产生具有一定频率的信号。通过向其施加直流电压,可以将该频率移至任一侧。因此,频率偏差与低通滤波器输出端的直流电压成正比。

进行上述操作,直到VCO频率等于输入信号频率为止。根据应用程序的类型,我们可以使用有源低通滤波器的输出或VCO的输出。 PLL被用于许多应用中,例如FM解调器,时钟发生器等。

PLL以以下三种模式之一运行–

- 自由运行模式

- 拍摄模式

- 锁定方式

最初,当没有输入输入时,PLL在自由运行模式下工作。当将具有某个频率的输入信号施加到PLL时,VCO的输出信号频率将开始变化。在此阶段,据说PLL在捕获模式下工作。 VCO的输出信号频率将连续变化,直到等于输入信号频率。现在,据说PLL在锁定模式下运行。

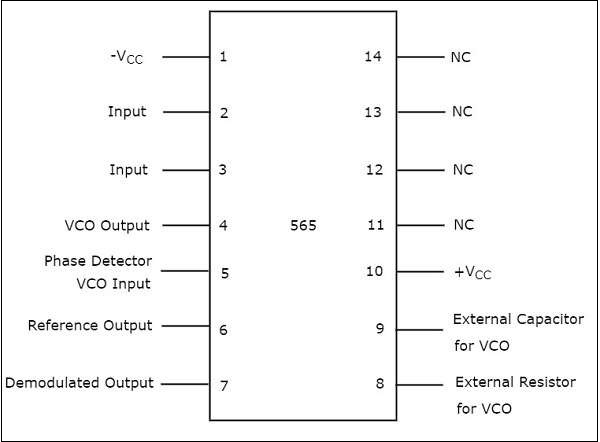

IC 565

IC 565是最常用的锁相环IC。它是一个14引脚双列直插式封装(DIP)。下图显示了IC 565的引脚图–

上图中每个引脚的用途不言而喻。在14个引脚中,只有10个引脚(引脚编号1至10)用于PLL的操作。因此,其余4个引脚(引脚号11至14)标记为NC(无连接)。

当引脚编号2和3接地时, VCO在IC 565的引脚编号4处产生输出。在数学上,我们可以将VCO的输出频率$ f_ {out} $写为。

$$ f_ {out} = \ frac {0.25} {R_VC_V} $$

哪里,

$ R_ {V} $是连接到引脚号8的外部电阻

$ C_ {V} $是连接到引脚号9的外部电容器

-

通过选择$ R_ {V} $和$ C_ {V} $的适当值,我们可以确定(确定)VCO的输出频率$ f_ {out} $。

-

引脚号4和5将通过外部导线短接,以便VCO的输出可用作相位检测器的输入之一。

-

IC 565的内部电阻为$ 3.6K \ Omega $。必须在引脚号7和10之间连接一个电容器C,以制造具有该内部电阻的低通滤波器。

请注意,根据要求,我们必须正确配置IC 565的引脚。