- 缓存一致性(1)

- 缓存一致性(1)

- 缓存一致性

- 缓存一致性和内存一致性的区别(1)

- 缓存一致性和内存一致性的区别

- 缓存一致性和内存一致性的区别

- 缓存一致性和内存一致性的区别(1)

- 一致性测试

- 一致性测试(1)

- 分布式数据库的最终一致性与强一致性

- 分布式数据库的最终一致性与强一致性(1)

- 分布式数据库中的最终一致性与强一致性

- 分布式数据库中的最终一致性与强一致性(1)

- 多处理器系统中的缓存一致性协议(1)

- 多处理器系统中的缓存一致性协议

- 一致性软件测试

- 一致性软件测试(1)

- Java同步-同步块示例

- 缓存 (1)

- 缓存(1)

- 空缓存 (1)

- 缓存

- ` 库缓存 (1)

- 同步java(1)

- Java中的同步

- Java中的同步(1)

- 同步块java(1)

- 同步块和同步方法示例之间的区别 (1)

- Java同步-静态同步示例

📅 最后修改于: 2020-12-13 15:22:04 🧑 作者: Mango

在本章中,我们将讨论缓存一致性协议,以解决多缓存不一致问题。

缓存一致性问题

在多处理器系统中,数据不一致可能发生在内存层次结构的相邻级别之间或同一级别内。例如,缓存和主存储器可能具有同一对象的不一致副本。

由于多个处理器并行运行,并且多个缓存可能独立拥有同一内存块的不同副本,因此会产生缓存一致性问题。高速缓存一致性方案通过为每个高速缓存的数据块保持统一状态来帮助避免此问题。

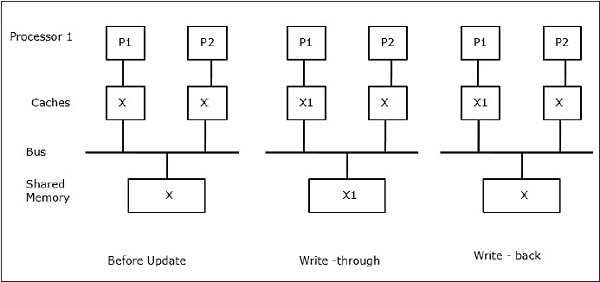

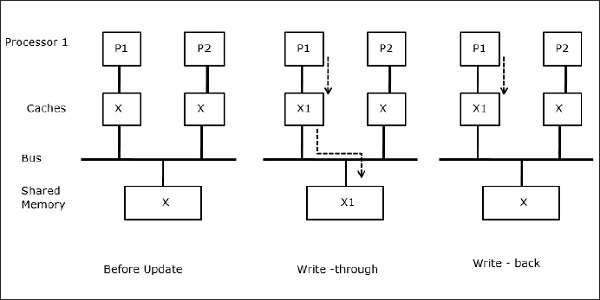

令X为共享数据的元素,已被两个处理器P1和P2引用。最初,X的三个副本是一致的。如果处理器P1通过使用直写策略将新数据X1写入缓存,则相同的副本将立即写入共享内存。在这种情况下,缓存和主内存之间会发生不一致。当使用回写策略时,当替换或无效缓存中的已修改数据时,将更新主内存。

通常,存在三个不一致问题的来源-

- 共享可写数据

- 流程迁移

- I / O活动

史努比总线协议

史努比协议通过基于总线的内存系统实现了缓存和共享内存之间的数据一致性。写入无效和写入更新策略用于维护高速缓存一致性。

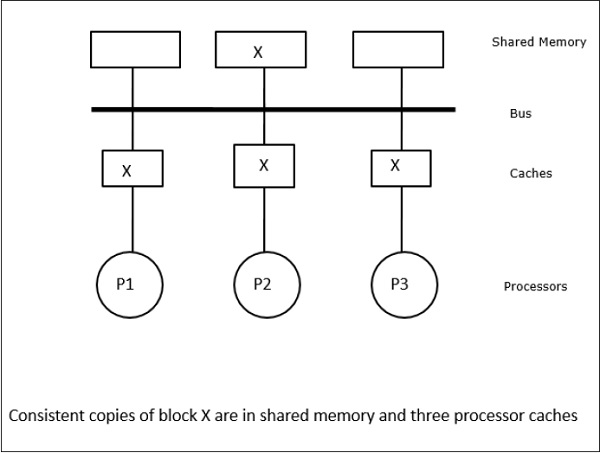

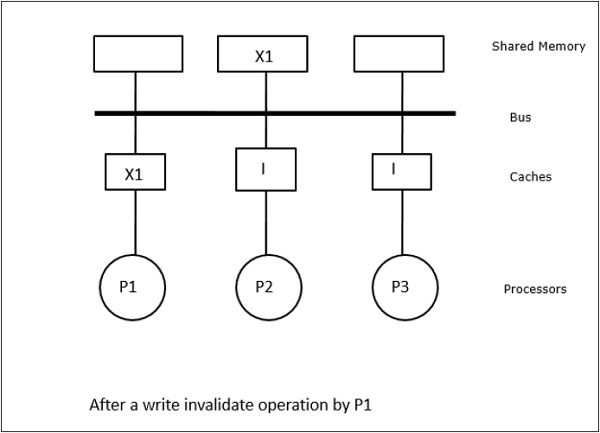

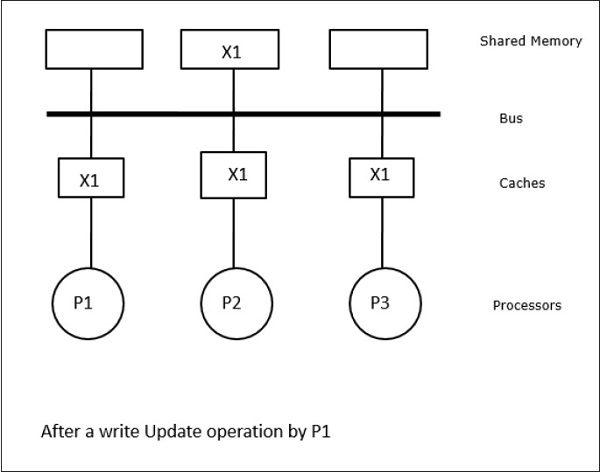

在这种情况下,我们有三个处理器P1,P2和P3,它们在其本地高速缓存和共享内存中具有数据元素“ X”的一致副本(图a)。处理器P1使用写入无效协议将X1写入其缓存中。因此,所有其他副本均通过总线无效。用“ I”表示(图b)。无效的块也称为脏块,即不应使用它们。写入更新协议通过总线更新所有缓存副本。通过使用回写缓存,还可以更新内存副本(图c)。

缓存事件和动作

在执行内存访问和无效命令时发生以下事件和动作-

-

读丢失-当处理器要读取一个块且该块不在高速缓存中时,将发生读丢失。这将启动总线读取操作。如果不存在脏副本,则具有一致副本的主内存将副本提供给发出请求的缓存。如果远程缓存中存在脏副本,则该缓存将限制主内存并将副本发送到发出请求的缓存中。在这两种情况下,高速缓存副本在读取未命中后将进入有效状态。

-

写入命中-如果副本处于脏状态或保留状态,则在本地完成写入,而新状态为脏状态。如果新状态有效,则将write-invalidate命令广播到所有缓存,从而使它们的副本无效。写入共享内存时,第一次写入后将保留结果状态。

-

写未命中-如果处理器无法在本地缓存中写入,则副本必须来自主内存或带有脏块的远程缓存。这是通过发送read-invalidate命令来完成的,该命令将使所有缓存副本无效。然后,本地副本将更新为脏状态。

-

读命中-读命中始终在本地缓存中执行,而不会导致状态转换或使用snoopy总线使之无效。

-

块替换-当副本脏时,应通过块替换方法将其写回主存储器。但是,当副本处于有效或保留或无效状态时,将不会进行替换。

基于目录的协议

通过使用多级网络来构建具有数百个处理器的大型多处理器,需要修改窥探式缓存协议以适合网络功能。在多级网络中进行广播非常昂贵,一致性命令仅发送到保留该块副本的那些高速缓存。这就是开发用于网络连接的多处理器的基于目录的协议的原因。

在基于目录的协议系统中,要共享的数据放置在一个公共目录中,该目录可维护缓存之间的一致性。在此,目录充当过滤器,处理器在其中请求许可权,以将条目从主内存加载到其缓存中。如果更改了条目,则目录将更新该条目或使该条目的其他缓存无效。

硬件同步机制

同步是一种特殊的通信方式,其中取代数据控制,而是在相同或不同处理器中的通信进程之间交换信息。

多处理器系统使用硬件机制来实现低级同步操作。大多数多处理器都具有硬件机制来施加原子操作,例如存储器读,写或读-修改-写操作,以实现某些同步原语。除了原子内存操作之外,一些处理器间中断也用于同步目的。

共享内存计算机中的缓存一致性

当处理器包含本地缓存时,在多处理器系统中维护缓存一致性是一个问题。在此系统中,不同缓存之间的数据不一致很容易发生。

主要关注领域是-

- 共享可写数据

- 流程迁移

- I / O活动

共享可写数据

当两个处理器(P1和P2)在其本地缓存中具有相同的数据元素(X),并且一个进程(P1)向数据元素(X)写入时,因为这些缓存是P1的直写本地缓存,因此主内存为也更新了。现在,当P2尝试读取数据元素(X)时,由于P2缓存中的数据元素已过时,因此找不到X。

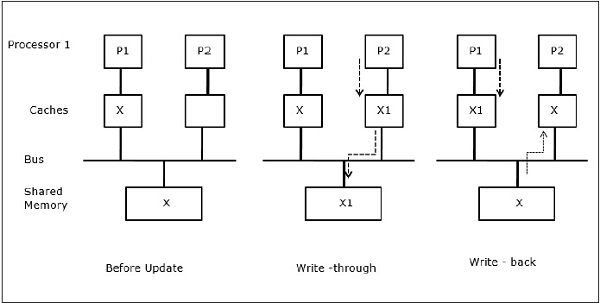

流程迁移

在第一阶段,P1的缓存具有数据元素X,而P2没有任何元素。 P2上的进程首先在X上写入,然后迁移到P1。现在,该过程开始读取数据元素X,但是由于处理器P1已过时的数据,该过程无法读取它。因此,P1上的进程将写入数据元素X,然后迁移到P2。迁移后,P2上的进程开始读取数据元素X,但它在主存储器中找到X的过时版本。

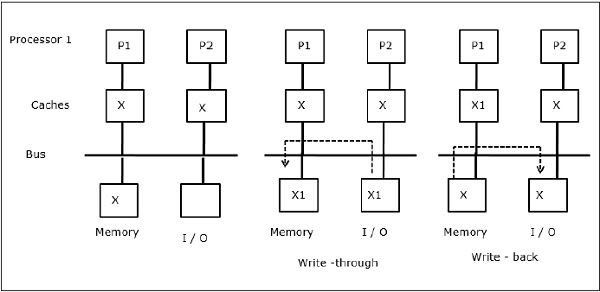

I / O活动

如图所示,I / O设备以两处理器多处理器体系结构添加到总线。首先,两个缓存都包含数据元素X。当I / O设备接收到新元素X时,它将直接将新元素存储在主存储器中。现在,当P1或P2(假设P1)尝试读取元素X时,它将获得过时的副本。因此,P1写入元素X。现在,如果I / O设备尝试传输X,它将得到一个过时的副本。

统一内存访问(UMA)

统一内存访问(UMA)架构意味着系统中所有处理器的共享内存都是相同的。普遍用于(文件)服务器的UMA计算机的流行类是所谓的对称多处理器(SMP)。在SMP中,处理器可以以统一的方式访问所有系统资源(如内存,磁盘,其他I / O设备等)。

非统一内存访问(NUMA)

在NUMA体系结构中,有多个具有内部间接/共享网络的SMP群集,这些群集连接在可伸缩的消息传递网络中。因此,NUMA体系结构是逻辑上共享的物理分布式内存体系结构。

在NUMA计算机中,处理器的缓存控制器确定内存引用是SMP内存本地还是远程。为了减少远程内存访问的次数,NUMA体系结构通常使用可以缓存远程数据的缓存处理器。但是,当涉及到缓存时,需要保持缓存一致性。因此,这些系统也称为CC-NUMA(缓存相干NUMA)。

仅缓存内存架构(COMA)

COMA机器与NUMA机器相似,唯一的区别是COMA机器的主存储器充当直接映射或组关联的缓存。数据块根据其地址散列到DRAM缓存中的某个位置。远程获取的数据实际上存储在本地主存储器中。此外,数据块没有固定的起始位置,它们可以在整个系统中自由移动。

COMA体系结构大多具有分层的消息传递网络。这样的树中的交换机包含一个目录,该目录具有数据元素作为其子树。由于数据没有起始位置,因此必须显式搜索。这意味着远程访问需要遍历树中的开关以在其目录中搜索所需数据。因此,如果网络中的交换机从其子树接收到针对同一数据的多个请求,它将把它们合并为一个请求,然后将其发送到交换机的父节点。当请求的数据返回时,交换机将在其子树中发送其多个副本。

COMA与CC-NUMA

以下是COMA和CC-NUMA之间的区别。

-

COMA往往比CC-NUMA更灵活,因为COMA无需操作系统即可透明地支持数据的迁移和复制。

-

COMA机器昂贵且构建复杂,因为它们需要非标准的内存管理硬件,并且一致性协议更难以实现。

-

COMA中的远程访问通常比CC-NUMA中的远程访问慢,因为需要遍历树形网络来查找数据。