- C / C++预处理器

- C++预处理器

- C / C++预处理器

- 宏处理器

- C预处理器

- C-预处理器(1)

- C-预处理器

- C C++预处理器(1)

- C预处理器(1)

- C++预处理器(1)

- 如何将数据转换为数值数据集 - Python 代码示例

- XSD-数值数据类型

- 如何将分类数据转换为数值数据 - R 编程语言(1)

- 如何将分类数据转换为数值数据 - R 编程语言代码示例

- 如何在python中将分类数据转换为数值数据(1)

- 数值数据类型以字符串形式返回 - TypeScript (1)

- 如何使用 JavaScript 处理多个数值数据集进行计算?(1)

- 如何使用 JavaScript 处理多个数值数据集进行计算?

- 如何在python代码示例中将分类数据转换为数值数据

- 数值数据类型以字符串形式返回 - TypeScript 代码示例

- 普通处理器和AI处理器的区别

- 普通处理器和AI处理器的区别(1)

- 什么是 HTML 预处理器?

- 什么是 HTML 预处理器?(1)

- XML-处理器(1)

- XML-处理器

- 普通处理器和AI处理器之间的区别

- 普通处理器和AI处理器之间的区别(1)

- 普通处理器和AI处理器之间的区别

📅 最后修改于: 2020-12-13 15:31:29 🧑 作者: Mango

8087数字数据处理器也被称为数学协处理器,数字处理器扩展和浮点单元。它是英特尔设计的首款可与8086/8088配对的数学协处理器,从而使计算更加轻松快捷。

一旦指令被8086/8088处理器识别,就将其分配给8087协处理器以进一步执行。

8087支持的数据类型是-

- 二进制整数

- 包装的十进制数字

- 实数

- 临时实格式

8087数字数据处理器的最显着特点如下-

-

它支持2-10字节之间的整数,浮点数和实数类型的数据。

-

处理速度如此之高,以至于它可以在〜27 µs内计算两个64位实数的乘积,并且还可以在〜35 µs内计算平方根。

-

它遵循IEEE浮点标准。

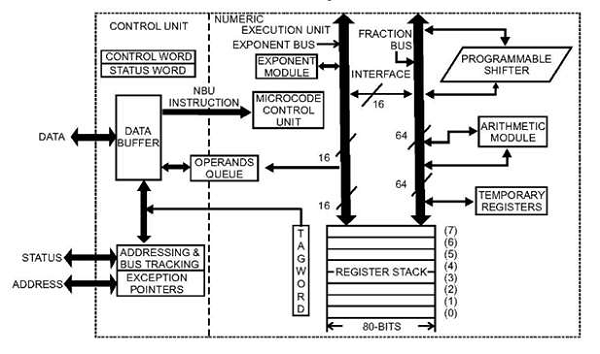

8087建筑

8087体系结构分为两组,即控制单元(CU)和数字扩展单元(NEU)。

-

控制单元处理处理器与内存之间的所有通信,例如接收和解码指令,读取和写入内存操作数,维护并行队列等。所有协处理器指令均为ESC指令,即它们以“ F”开头,协处理器仅执行ESC指令,而其他指令则由微处理器执行。

-

数字扩展单元处理所有数字处理器指令,例如算术,逻辑,先验和数据传输指令。它具有8个寄存器堆栈,其中包含指令及其结果的操作数。

8087协处理器的架构如下-

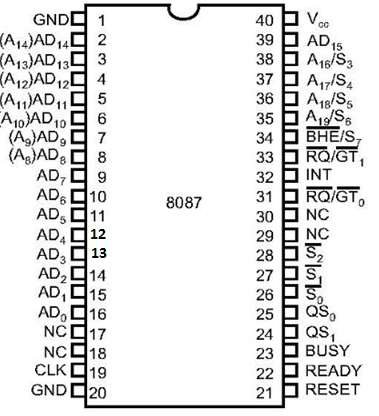

8087引脚说明

让我们首先看一下8087的引脚图-

下表提供了8087的引脚说明-

-

AD 0 – AD 15 –这些是时间复用的地址/数据线,在第一个时钟周期内承载地址,从第二个时钟周期起承载数据。

-

A 19 / S 6 – A 16 / S-这些线是时间复用的地址/状态线。它的功能类似于8086的相应引脚。S 6 ,S 4和S3始终为高,而S 5始终为低。

-

$ \ overline {BHE} $ / S 7-在第一个时钟周期中,$ \ overline {BHE} $ / S 7用于将数据启用到8086数据总线的高字节,之后作为状态行S 7 。

-

QS 1 ,QS 0-这些是队列状态输入信号,提供指令队列的状态,其条件如下表所示-

| QS0 | QS1 | Status |

|---|---|---|

| 0 | 0 | No operation |

| 0 | 1 | First byte of opcode from the queue |

| 1 | 0 | Empty the queue |

| 1 | 1 | Subsequent byte from the queue |

-

INT-这是一个中断信号,当在执行过程中收到未屏蔽的异常时,它将变为高电平。

-

忙-这是一个输出信号,当它为高电平时,它指示CPU处于忙状态。

-

就绪-这是一个输入信号,用于通知协处理器总线是否已准备好接收数据。

-

RESET-这是一个输入信号,用于拒绝协处理器的内部活动,并在CPU需要时为进一步执行做准备。

-

CLK -CLK输入提供处理器操作的基本时序。

-

VCC-这是一个电源信号,需要+ 5V的电源才能使电路工作。

-

S 0 ,S 1 ,S 2-这些是提供操作状态的状态信号,总线控制器8087使用这些状态信号生成内存和I / O控制信号。这些信号在第四个时钟周期内有效。

| S2 | S1 | S0 | Queue Status |

|---|---|---|---|

| 0 | X | X | Unused |

| 1 | 0 | 0 | Unused |

| 1 | 0 | 1 | Memory read |

| 1 | 1 | 0 | Memory write |

| 1 | 1 | 1 | Passive |

-

RQ / GT 1和RQ / GT 0-这些是8087处理器用于从主处理器8086/8088获得总线控制权以进行操作数传输的请求/授权信号。