8086处理器提供16位数据总线。因此它能够在一个周期内传输16位,但是每个存储位置只有一个字节(8位),因此我们需要两个周期才能从两个不同的存储位置访问16位(每个8位)。解决此问题的方法是存储库。通过存储库,我们的目标是在一个周期内访问两个连续的存储单元(传输16位)。

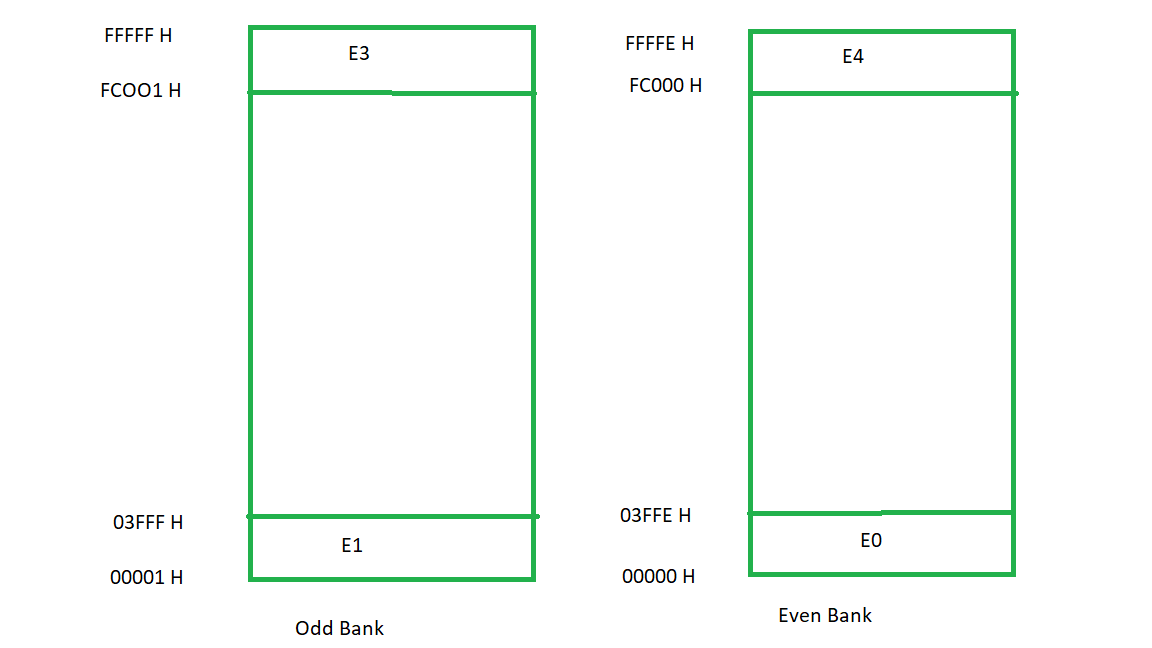

存储芯片平均分为两部分(存储体)。其中一个存储区包含偶数地址,称为偶数存储区,另一个存储区包含奇数地址,称为奇数存储区。偶数存储区始终提供低位字节,因此偶数存储区也称为低位存储区(LB),奇数存储区也称为高位存储区(HB)。

这种存储方案允许同时访问两个存储区中两个对齐的内存位置并处理16位数据传输。内存存储并不需要强制传输16位数据,而是简化了16位数据传输的过程。

8位和16位传输之间的选择取决于程序员给出的指令。

例子:

地址的最低有效位(A 0不用于字节选择)保留用于存储体选择。因此,A 0 = 0将选择偶数库。 BHE信号用于选择奇数存储区。处理器将使用这两个信号的组合来决定数据传输的类型。

| BHE | A0 | types of Transfer |

|---|---|---|

| 0 | 0 | 16 bit data transfer from both HB and LB |

| 0 | 1 | 8 bit data transfer from HB |

| 1 | 0 | 8 bit data transfer from LB |

| 1 | 1 | None(Idle) |

在这种情况下,第一个机器周期产生奇数地址(A 0 = 1)在高阶数据总线上传输低8位数据位。在第二个机器周期内,高阶数据总线将在低阶数据总线上传输。