问题–绘制以下代码的时序图,

MVI B, 45 命令说明–将立即8位数据存储到寄存器或存储器位置。

例如:MVI B,45岁

操作码:MVI

操作数:B是目标寄存器,而45是需要传输到寄存器的源数据。

“ 45”数据将存储在B寄存器中。

算法 –

- 确定什么是操作码,什么是数据。此处,操作码为“ MVI B”,数据为45。

- 假定操作码和数据的存储地址。例如:

MVI B, 452000: Opcode2001: 45 - 所有指令中的操作码提取均相同。

- 仅需要在连续的T状态中添加操作码的读取指令。

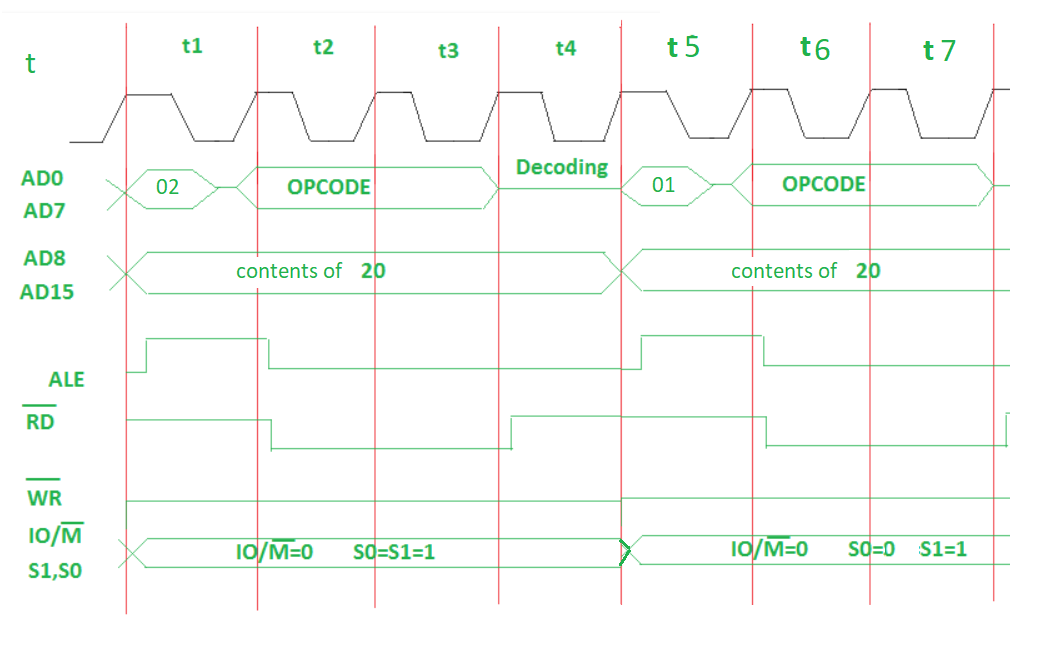

- 对于操作码提取,IO / M(低有效)= 0,S1 = 1和S0 =1。此外,从内存中提取操作码将需要4个T状态。

- 对于操作码读取,IO / M(低电平有效)= 0,S1 = 1和S0 =0。此外,从存储器读取数据仅需要3个T状态。

在操作码提取(t1-t4 T状态)中–

- 00 –存储操作码的地址的低位。

- 20 –存储操作码的地址的高位。

- ALE –为多路复用地址和数据总线提供信号。仅在t1中,它用作地址总线以获取地址的低位,否则它将用作数据总线。

RD(低有效)– t1和t4中的信号为1,微处理器未读取任何数据。在t2和t3中,信号为0,微处理器读取数据。

WR(低有效)–信号始终为1,微处理器不写入任何数据。

IO / M(低有效)–信号始终为0,正在存储器中执行操作。

S0和S1 –在t1到t4状态下信号为1,以便从内存中获取操作码。

在操作码中读取(t5-t7 T状态)–

- 01 –存储数据的地址的低位。

- 20 –存储数据的地址的高位。

- ALE –为多路复用地址和数据总线提供信号。仅在t5中,它用作地址总线以获取地址的低位,否则它将用作数据总线。

RD(低有效)– t5中的信号为1,因为微处理器未读取任何数据。由于微处理器读取了数据,因此在t6和t7中信号为0。

WR(低有效)–信号始终为1,微处理器不写入任何数据。

IO / M(低有效)–信号始终为0,正在存储器中执行操作。

S0 –信号始终为0,正在对存储器执行操作以读取数据45。

S1 –信号始终为1,正在对存储器执行操作以读取数据45。