在本文中,我们将讨论同步受控计数器的概述,并将详细讨论其电路图、电路激励表、时序图。让我们一一讨论。

概述 :

触发器或D型触发器可用于制作同步计数器,并且比异步计数器更容易设计。由于触发器的时钟输入都是一起计时的,并且同时具有相同的时钟信号,这就是为什么它被称为同步计数器。它也被称为并行计数器,因为时钟并行馈送到所有触发器。

先决条件——

设计同步计数器和以下先决条件如下。

- 在这种类型的计数器模式中应用控制输入。

- 模式控制输入决定哪个序列后跟一个计数器。

- 设计过程与同步计数器设计相同。

- 任何类型的 FF 均可用于此类设计。

例子 :

考虑可以对模 4 或模 8 进行计数的计数器由模式控制输入(例如 S)决定。如果 S= 0,那么它将作为 mod 4 计数器工作,如果 S=1 它将执行向下计数。

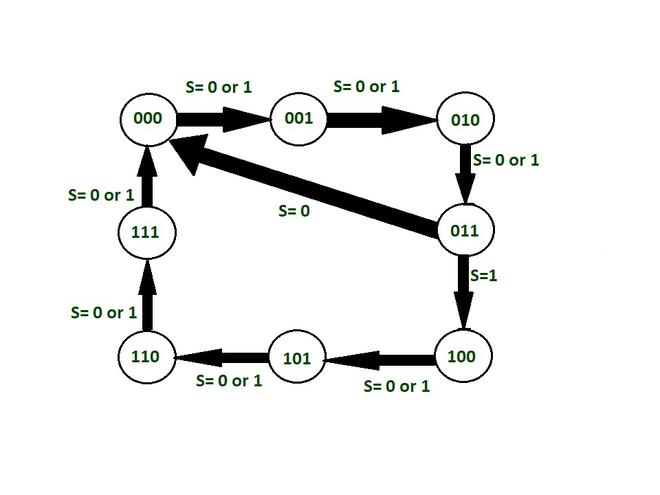

- 对于这种类型的计数器的设计,2 3 = 8(因为计数到 7 需要 3 位),即需要三个 FF。这里使用了 T FF。状态图如下图所示。

- 在这种情况下,如果计数器状态低于 011,则 S 的值可以是 0 或 1,因为在 mod -4 或 mod 8 中,直到 011 的计数序列在两种情况下都是相同的。因此 S 的值可以是 0 或 1。如果 S= 0,则从 011 到 000 的转换发生并且计数器将重置。如果 S=1,就会发生从 011 到 100 的转换。之后,S 的值可以是 0 或 1,直到状态 000 出现。

电路励磁表:

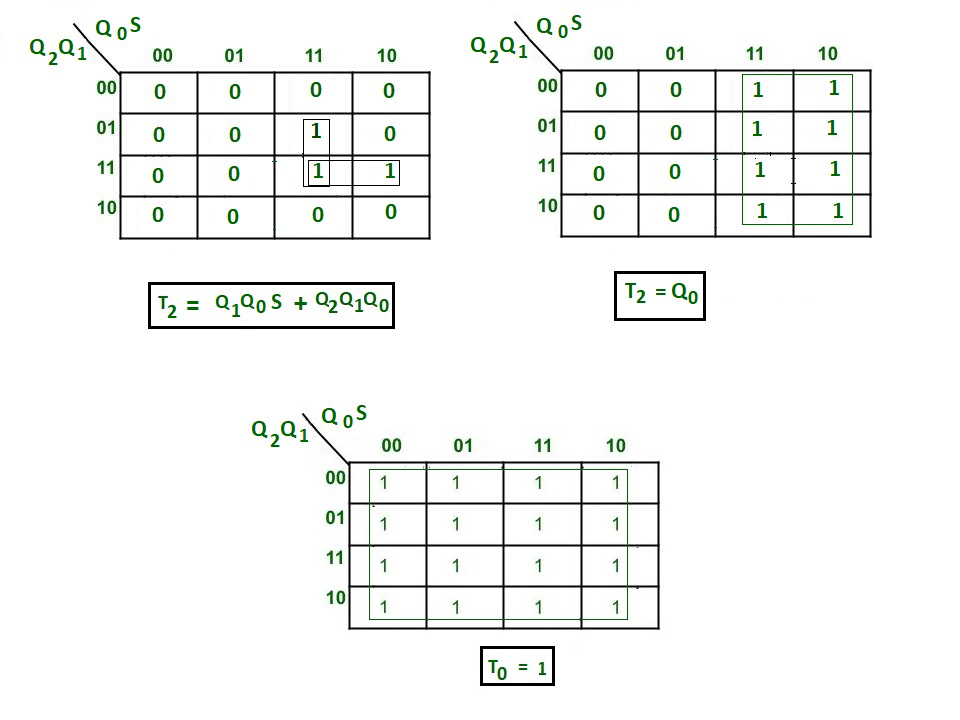

它显示了 FF 的当前状态和应用时钟脉冲和输入值后的下一个状态。这里使用了 T FF。所以FF的T(toggle)输入的值只有当对应的状态输出值从0变为1或1变为0时才为1,否则保持不变。下表是根据所需的计数顺序。

Q - means Present state

Q* - means next state.

在这里,我们使用 K 映射找出 3 个触发器的输入变量的最小布尔表达式。

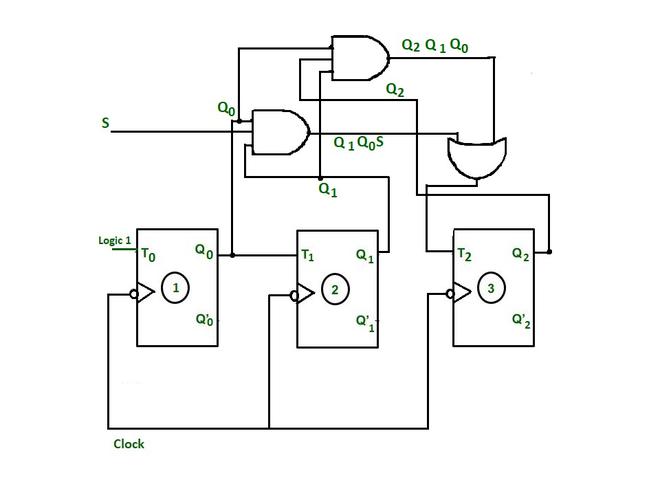

电路图 :

这里的电路是为我们已经得到的表达式实现的。电路输出顺序与状态图所示相同。

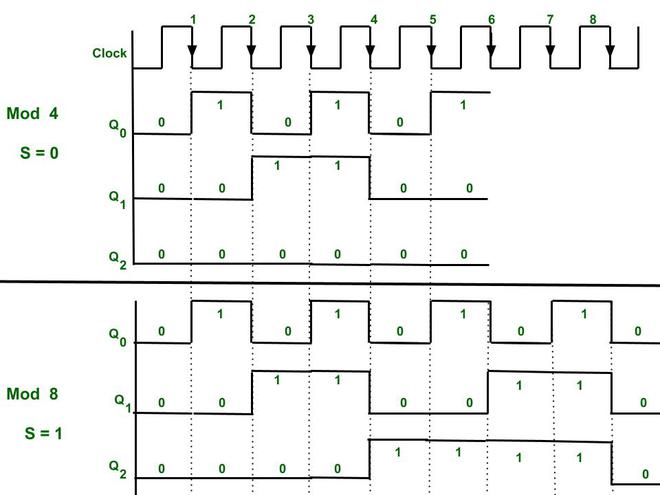

时序图:

可以从时序图验证计数器的顺序。如果计数器复位且控制输入 S 为 0,则它将遵循 mod-4 的序列,即它将计数 000、001、010、011 并重复。如果计数器复位且控制输入 S 为 1,则计数器将计数序列 000、001、010、011、100、101、110、111,并重复。

案例1 :

当 S= 0 时,在第 4 个边沿触发时钟脉冲后。

- 当Q 2 =0、Q 1 = 1、Q 0 = 1且S=0时,即第3个边缘时钟脉冲后的3FF状态。

- 将这些代入表达式 T2 = Q 2 Q 1 Q 0 + SQ 1 Q 0 = 0+0 =0,然后在第 4 个边沿触发的时钟脉冲 FF 3 后保留其状态,即 Q 2 = 0

- T 1 = Q 0 = 1,因此 FF 2 切换其输出状态,即 Q1 变为 0

- T 0 = 1,因此 FF 1 切换其输出状态,即 Q 0变为 0

- Q 2 Q 1 Q 0在第 4 个负时钟 0 0 0 之后变为十进制等效值为 0

- 因此从 110 到 000(复位)的转变发生在第 4 个 -Ve 边沿之后。

案例2 :

当 S=1 时,在第 4 个边沿触发的时钟脉冲之后。

- 当Q 2 =0、Q 1 = 1、Q 0 = 1且S = 1时,即第3个边沿时钟脉冲后3FF的状态。

- 将这些放入表达式 T2 = Q 2 Q 1 Q 0 + SQ 1 Q 0 = 0+1= 1,然后在第 4 个边缘时钟脉冲 FF 3 保留其切换其输出状态,即 Q 2变为 1。

- T 1 = Q 0 = 1,因此 FF 2 切换其输出状态,即 Q 1变为 0

- T 0 = 1,因此 FF 1 切换其输出状态,即 Q 0变为 0

- Q 2 Q 1 Q 0在第 4 个负时钟 1 0 0 时变为十进制等效值为 4

mod-4 或 mod-8 计数器的时序图

说明:

这里 -Ve 边沿触发用于切换目的。

- 由于 T1= Q 0 。因此,只有在出现下降沿(即使用-ve 边沿触发时钟)且Q 0 =1 时,FF 1 的输出状态才会发生变化,然后发生翻转,T1 的输出状态将发生变化。

- 由于 T2 = Q 1 Q 0 S+ Q 2 Q 1 Q 0 。如果 S= 0,则 FF 2 的输出状态仅在 Q 2 Q 1 Q 0将导致 1 并且存在下降沿时才会改变,否则状态将被保留。

- 如果 S= 1,T2 = Q 1 Q 0 + Q 2 Q 1 Q 0 ,因此当 Q 1 Q 0结果为 1 或 Q 2 Q 1 Q 0结果为 1 并且有时钟下降沿时,FF 3 的输出状态将发生变化.

- 因此,在每个 -Ve 边沿时钟脉冲,输出状态都会改变。