高速缓存内存性能

缓存类型:

- L1 缓存: CPU 本身内置的缓存称为 L1 或 1 级缓存。这种类型的高速缓存保存最新的数据,因此当再次需要数据时,微处理器首先检查此高速缓存,因此它不需要通过主存储器或二级高速缓存。上述概念背后的主要意义是“参考位置”,根据这一概念,CPU 刚刚访问的位置有更高的概率再次被需要。

- L2 缓存:这种类型的缓存位于 CPU 旁边的单独芯片上,也称为 2 级缓存。此缓存存储在 L1 缓存中找不到的最近使用的数据。一些 CPU 具有内置的 L1 和 L2 缓存,并将单独的缓存芯片指定为 3 级 (L3) 缓存。

内置在 CPU 中的缓存比单独的缓存更快。单独的缓存比 RAM 快。内置高速缓存以微处理器的速度运行。

- 磁盘缓存:它包含最近从硬盘读取的数据,此缓存比 RAM 慢得多。

- 指令缓存与数据缓存:指令或 I-cache 仅存储指令,而 Data 或 D-cache 仅存储数据。通过这种方法区分存储的数据可以识别指令和数据的不同访问行为模式。例如:程序需要很少的写访问,并且它们通常比它们处理的数据表现出更多的时间和空间局部性。

- 统一缓存与拆分缓存:存储指令和数据的缓存称为统一缓存。另一方面,拆分缓存由两个相关但很大程度上独立的单元组成——I-cache 和 D-cache。这种类型的缓存也可以设计为以不同的方式处理两个独立的单元。

高速缓存的性能是用一个称为命中率的量来衡量的。当 CPU 引用内存并显示缓存中的单词时,就说明命中已成功发生。如果在高速缓存中没有发现这个词,那么 CPU 会为喜欢的词引用主存储器,这被称为缓存未命中。

- 命中率 (h) :

Hit Ratio (h) = Number of Hits / Total CPU references to memory = Number of hits / ( Number of Hits + Number of Misses )

命中率只不过是从 CPU 进行的一些内存引用中获得命中的概率。所以它的范围是0 <= h <= 1 。

- 平均访问时间(t avg ):

tavg = h X tc + ( 1- h ) X ( tc + tm ) = tc + ( 1- h ) X tm

令t c 、 h和t m分别表示缓存访问时间、缓存命中率和主访问时间。

平均内存访问时间 = 命中时间 + 未命中率 X 未命中惩罚

未命中率:它可以定义为不在缓存中的访问的一部分(即(1-h))。

Miss Penalty :它可以定义为为未命中服务而增加的时钟周期,即在缓存未命中的情况下将偏好信息从主存储器传送到缓存所需的额外时间。

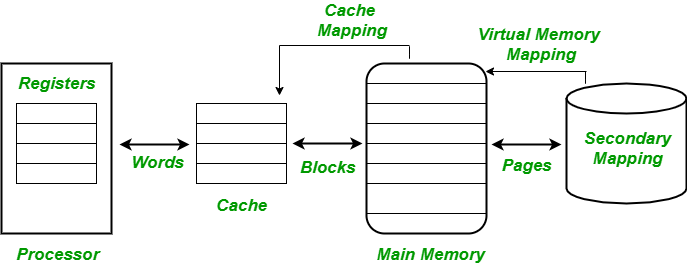

缓存内存结构

缓存未命中的类型:

- Compulsory Miss (Cold start Misses 或 First reference Misses) :这种类型的未命中发生在第一次访问块时发生。在这种类型的未命中中,必须将块放入缓存中。

- 容量缺失:当程序工作集远大于缓存存储容量时,就会发生这种类型的缺失。需要丢弃块,因为在程序执行期间不可能保留所有块。

- 冲突缺失(碰撞缺失或干扰缺失):这种缺失主要出现在集合关联或直接映射块放置策略的情况下,当多个块映射到同一集合或块帧时会发生冲突缺失。

- Coherence Miss (Invalidation) :当其他外部处理器(例如 I/O)更新内存时发生。

中央处理器性能:

CPU 时间分为用于执行包/程序的时钟周期和用于等待内存系统的时钟周期。缓存命中是常规 CPU 周期的一部分。

CPU time = ( CPU execution clock cycles + memory stall clock cycles ) X Clock Cycle time

1. Memory Stall Clock 周期(用于回写缓存):

- 内存停止时钟周期 = 读取停止周期 + 写入停止周期

- 读写周期 = ( 读/程序 ) X 读未命中率 X 读未命中惩罚

- 写停顿周期 = ( 写/程序 ) X 写未命中率 X 写未命中惩罚 + 写缓冲区停顿

2. Memory Stall Clock 周期(用于直写缓存):

- 假设写缓冲区停顿可以忽略不计。每次访问(读/写)都类似处理。

- 内存停顿时钟周期 =(内存访问/程序)X 未命中率 X 未命中惩罚

- 内存停顿时钟周期 =(指令/程序)X(未命中/指令)X 未命中惩罚

测量和提高缓存性能:

1. 用于最小化平均内存访问时间的技术:

- 减少命中时间、未命中惩罚或未命中率。

- 减少未命中惩罚 X 未命中率。

2. 减少命中时间的技巧:

- 小而简单的缓存。

- 跟踪缓存和流水线缓存访问

- 避免地址转换的时间损失。

3. 减少漏罚的技巧:

- 多级缓存的使用。

- 优先读取未命中而不是写入。

- 受害者缓存

4. 降低 Miss Rate 的技巧:

- 增加块大小

- 更高的关联性。

- 编译器优化

- 大缓存。

5. 减少技巧(Miss Rate X Miss Penalty):

- 非阻塞缓存

- 硬件预取

- 编译器控制的预取