- 使用DMA控制器8257/8237进行直接存储器访问

- DMA控制器的内部寄存器

- DMA控制器的内部寄存器(1)

- 微处理器

- 微处理器(1)

- 微处理器 (1)

- 微处理器与微处理器

- 微处理器(µC)和微处理器(µP)有什么区别?

- 微处理器(µC)和微处理器(µP)有什么区别?(1)

- 计算机体系结构中的直接访问媒体(DMA)控制器(1)

- 计算机体系结构中的直接访问媒体(DMA)控制器

- 计算机体系结构中的直接访问媒体(DMA)控制器

- 计算机体系结构中的直接访问媒体(DMA)控制器(1)

- 微处理器 - 任何代码示例

- DMA传输模式

- DMA传输模式(1)

- c# 控制器 - C# (1)

- 微处理器中的存储区

- 微处理器中的存储区(1)

- 微处理器教程(1)

- 微处理器教程

- 使用DMA控制器82578237进行直接存储器访问(1)

- c# 控制器 - C# 代码示例

- 讨论微处理器(1)

- 讨论微处理器

- 微处理器-概述(1)

- 微处理器-概述

- I / O接口(中断和DMA模式)

- I/O 接口(中断和 DMA 模式)

📅 最后修改于: 2020-12-13 15:33:00 🧑 作者: Mango

DMA代表直接内存访问。它由英特尔设计,以最快的速度传输数据。它允许设备直接在内存中传输数据,而不会受到CPU的干扰。

该设备使用DMA控制器,请求CPU保持其数据,地址和控制总线,因此该设备可以自由地直接向/从存储器传输数据。仅在从CPU接收到HLDA信号后,才启动DMA数据传输。

DMA操作如何执行?

以下是DMA执行的操作序列-

-

最初,当任何设备必须在设备和内存之间发送数据时,设备必须向DMA控制器发送DMA请求(DRQ)。

-

DMA控制器将保持请求(HRQ)发送到CPU,并等待CPU声明HLDA。

-

然后,微处理器将所有数据总线,地址总线和控制总线置于三态。 CPU离开对总线的控制,并通过HLDA信号确认HOLD请求。

-

现在,CPU处于保持状态,并且DMA控制器必须通过CPU,内存和I / O设备之间的总线来管理操作。

8257的特点

这是8257的一些突出功能的列表-

-

它具有四个通道,可以在四个I / O设备上使用。

-

每个通道都有16位地址和14位计数器。

-

每个通道最多可以传输64kb的数据。

-

每个通道均可独立编程。

-

每个通道可以执行读传输,写传输和验证传输操作。

-

它会向外围设备生成MARK信号,表明已传输了128个字节。

-

它需要一个单相时钟。

-

其频率范围为250Hz至3MHz。

-

它以两种模式运行,即主模式和从模式。

8257建筑

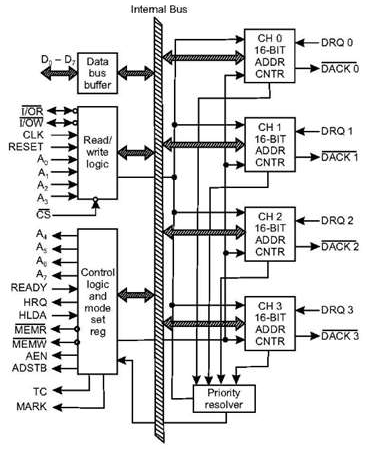

下图显示了8257的体系结构-

8257引脚说明

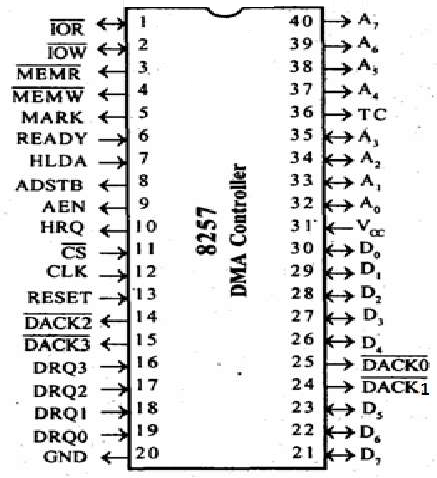

下图显示了8257 DMA控制器的引脚图-

DRQ 0 -DRQ 3

这些是四个单独的通道DMA请求输入,外围设备使用它们来使用DMA服务。当选择固定优先级模式时,其中DRQ 0具有最高优先级,而DRQ 3具有最低优先级。

DACK o -DACK 3

这些是低电平有效的DMA确认线,用于更新请求外围设备的CPU请求状态。这些线也可以用作请求设备的选通线。

D o -D 7

这些是双向数据线,用于将系统总线与DMA控制器的内部数据总线接口。在从模式下,它携带命令字到8257和状态字从8257。在主模式下,这些行用于将生成的地址的高字节发送到锁存器。该地址使用ADSTB信号进一步锁存。

IOR

它是低电平有效的双向三态输入线,CPU在从模式下用于读取8257的内部寄存器。在主模式下,它用于在存储器写入周期中从外围设备读取数据。

OW

它是一条低电平有效的双向三态线,用于将数据总线的内容加载到8位模式寄存器或16位DMA地址寄存器或终端计数寄存器的高/低字节。在主模式下,它用于在DMA存储器读取周期内将数据加载到外围设备。

时钟

这是8257内部操作所需的时钟频率信号。

重启

该信号用于通过禁用所有DMA通道来复位DMA控制器。

A o -A 3

这是四个最低有效地址线。在从模式下,它们充当输入,选择要读取或写入的寄存器之一。在主模式下,它们是8257生成的四个最低有效内存地址输出线。

CS

这是一个低电平有效的片选线。在从模式下,它启用对8257的读/写操作。在主模式下,它禁用对8257的读/写操作。

A 4 -A 7

这些是主模式下DMA生成的低字节地址的高半字节。

准备

这是一个高电平有效的异步输入信号,它通过插入等待状态使DMA准备就绪。

人力资源问卷

该信号用于从输出设备接收保持请求信号。在从模式下,它与DRQ输入线8257连接。在主模式下,它与CPU的HOLD输入连接。

HLDA

保持确认信号表示DMA控制器,当总线控制器设置为1时,总线已被CPU授予请求外围设备。

记忆体

它是低位存储器读取信号,用于在DMA读取周期内从寻址的存储器位置读取数据。

兆瓦

它是低电平有效的三态信号,用于在DMA写操作期间将数据写到寻址的存储器位置。

广告

该信号用于将DMA控制器生成的存储器地址的高字节转换为锁存器。

AEN

该信号用于禁用地址总线/数据总线。

TC

它代表“ Terminal Count”(终端计数),它表示到当前外围设备的当前DMA周期。

标记

该标记将从头开始每128个循环或其整数倍后被激活。它指示当前的DMA周期是自上一个MARK输出到所选外围设备以来的第128个周期。

V CC

电源信号是电路工作所需的。