超大规模集成电路设计周期

超大规模集成 (VLSI) 是通过在单个芯片上组合电阻、晶体管和电容器等许多组件来制造集成电路 (IC) 的过程。

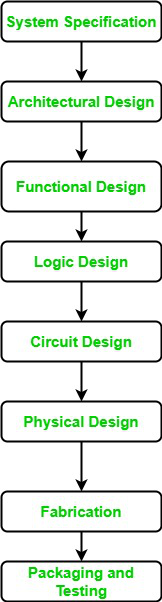

VLSI 设计是一个迭代循环。设计超大规模集成电路芯片包括功能设计、逻辑设计、电路设计和物理设计等几个问题。通过仿真过程验证设计的准确性。如果在验证的任何阶段发现任何设计错误,则必须在设计过程中重复至少一个先前的设计步骤以纠正错误。

VLSI设计流程图说明:

超大规模集成电路设计周期

1.系统规格:在这一步中写出所需最终产品的目标。在系统规范期间,系统的指定成本、其性能、体系结构以及系统将如何与外部世界进行通信都将被确定。在此步骤中,设计规范应由用户或客户提供。

2、架构设计:所需设计的基本架构必须满足所需设计的系统规范。所需设计的架构已确定,其布局由设计工程师设计。架构设计包括模拟和混合信号模块的集成、内存管理、内部和外部通信、电源要求以及工艺技术和层堆栈的选择。

3. 功能设计或行为设计:它包括细化所需设计的设计规范,以设计所需系统的功能行为。其主要目标是在规范提出的成本要求内生成高性能架构设计。

4. 逻辑设计:在这一步中,将所需设计的结构添加到所需设计的行为表示中。逻辑设计要考虑的主要规范是逻辑最小化、性能增强和可测试性。逻辑设计还必须考虑与测试向量生成、错误检测和错误纠正相关的问题。已经开发了许多逻辑综合工具用于逻辑设计过程的自动化。

5. 电路设计:在此步骤中,将所需设计的逻辑块替换为由电阻器、电容器和晶体管等电子器件组成的电子电路。在此阶段完成所需设计的电路仿真,以验证所需系统的时序行为。基尔霍夫定律用于了解电子电路在节点电压和分支电路方面的行为。然后在离散时间求解积分微分方程的结果。 SPICE 是著名的电路仿真程序。

6. 物理设计:在这一步中,完成了所需系统的实际布局,其中所有组件都将放置在电路中,并且所有这些组件都相互连接。所需系统的实际布局会影响最终所需产品的面积、正确性和性能。芯片的正确性也受物理设计的控制。通过电路模拟器测试的电路设计在封装后可能会出现故障。这是因为几何设计规则错误。必须遵循这些设计规则,以确保芯片制造的正确性。如果不遵守设计规则,可能会导致短路、开路、开路等错误。

7. 制造:在实际布局和验证所需设计后,将设计送去制造。将所需设计移交给制造过程称为流片。用于制造的数据的生成称为流出。使用光刻工艺将所需的设计放在设计的不同层上。 IC 是在直径从 200 毫米到 300 毫米的圆形硅晶片上制造的,然后对这些 IC 进行测试并标记为功能性或有缺陷的 IC。

8、封装测试:设计完成后,封装功能芯片。封装在所需的设计过程和应用程序的早期配置,以及成本和外形尺寸要求。封装类型可能包括双列直插式封装 (DIP)、针栅阵列 (PGA) 和球栅阵列 (BGA)。在管芯定位在封装腔中之后,其引脚连接到封装的引脚,例如,通过引线键合或固体凸块(倒装芯片)。然后密封所需设计的包装,然后发送给最终用户或客户。