并行随机存取机(也称为PRAM )是大多数并行算法都考虑使用的模型。它有助于编写没有任何体系结构约束的前体并行算法,并且还允许并行算法设计人员将处理能力视为无限。它忽略了进程间通信的复杂性。 PRAM算法主要是理论上的,但可以用作开发适用于实际机器的高效并行算法的基础,也可以激励建造专用机器。

PRAM体系结构模型:以下是PRAM组成的模块:

- 它由一个控制单元,全局存储器和一组无限的相似处理器组成,每个处理器都有自己的专用存储器。

- 活动处理器从全局存储器读取,执行所需的计算,然后写入全局存储器。

- 因此,如果PRAM中有N个处理器,则可以在特定时间单位内执行N个独立操作。

PRAM的模型:在访问共享内存时,在执行读写操作时可能会发生冲突(即,一个处理器可以访问另一个处理器已经在访问的内存块)。因此,PRAM模型上存在各种约束,这些约束可以处理读取或写入冲突。他们是:

- EREW:也称为互斥读取互斥写入是一个约束,不允许两个处理器在同一实例中从同一内存位置进行读取或写入。

- CREW:也称为“并发读独占写入”是一种约束,它允许所有处理器从同一内存位置读取,但不允许同时写入同一内存位置。

- ERCW:也称为“排他读取并发写入”是一种约束,它允许所有处理器写入同一内存位置,但现在允许同时读取同一内存位置。

- CRCW:也称为并发读取并发写入是一种约束,它允许所有处理器并行地读取和写入相同的内存位置。

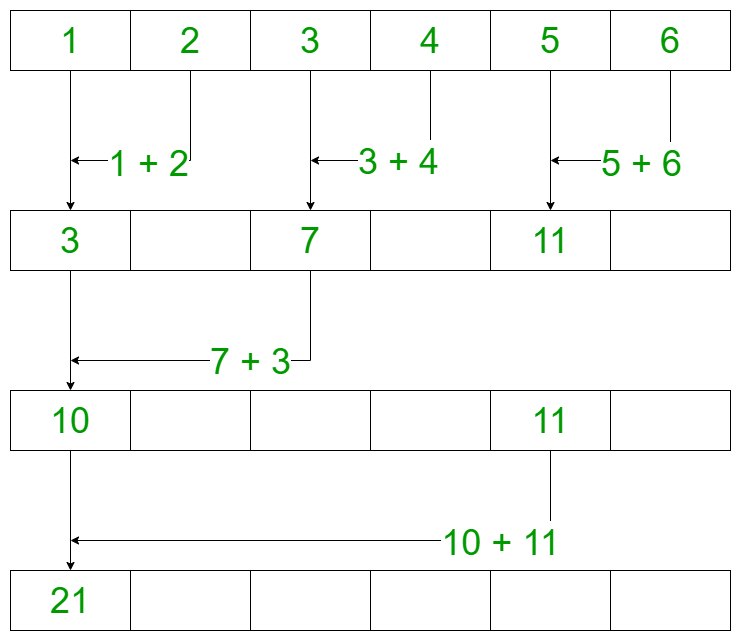

示例:假设我们希望添加一个由N个数字组成的数组。通常,我们遍历数组,并使用N个步骤查找数组的总和。因此,如果数组的大小为N,并且对于每一步,我们假设花费的时间为1秒。因此,需要N秒才能完成迭代。使用PRAM的CRCW模型可以更有效地执行相同的操作。假设有一个N / 2个并行处理器用于大小为N的数组,那么执行时间为4,在下图中,该时间小于N = 6秒。