先决条件–逻辑门简介

使用VHDL(VHSIC硬件描述语言)编程语言设计和实现AND和OR逻辑门。

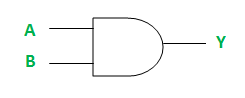

1. AND门的逻辑开发:

AND逻辑门可以如下实现–

AND Gate的真值表为:

| A | B | Y = A AND B |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

执行 –

以下是上述逻辑在VHDL语言中的实现。

-- VHDL Code for AND gate

-- Header file declaration

library IEEE;

use IEEE.std_logic_1164.all;

-- Entity declaration

entity andGate is

port(A : in std_logic; -- AND gate input

B : in std_logic; -- AND gate input

Y : out std_logic); -- AND gate output

end andGate;

-- Architecture definition

architecture andLogic of andGate is

begin

Y <= A AND B;

end andLogic; 2.或门的逻辑开发:

或逻辑门可以实现如下:

OR Gate的真值表为:

| A | B | Y = A OR B |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

执行 –

以下是上述逻辑在VHDL语言中的实现。

-- VHDL Code for OR gate

-- Header file declaration

library IEEE;

use IEEE.std_logic_1164.all;

-- Entity declaration

entity orGate is

port(A : in std_logic; -- OR gate input

B : in std_logic; -- OR gate input

Y : out std_logic); -- OR gate output

end orGate;

-- Architecture definition

architecture orLogic of orGate is

begin

Y <= A OR B;

end orLogic;