- 在各种数字应用中(例如:有线控制单元),需要控制信号以特定的时间顺序启动,执行和步进各种操作。

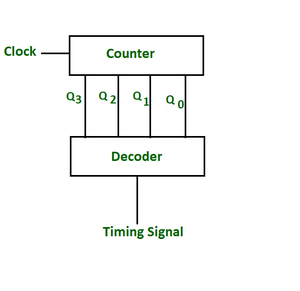

- 为此,需要控制信号并且为了生成控制信号,设计了计数器电路,其输出连接到解码器。解码器提供所需的控制信号。

- 计数器可以是同步的或异步的。

- 设计计数器的过程与相同的参考(本)。

产生控制信号的方框图

通过考虑示例可以理解控制信号的设计。

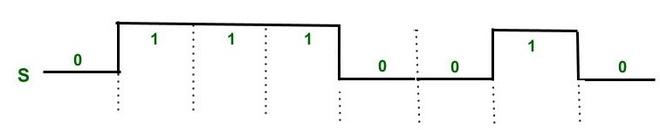

示例–生成一个控制信号,该信号可以传递以下脉冲序列。脉冲序列将在7个脉冲后重复。

控制信号

在这里,我们需要生成一个控制信号(例如S),该信号可以生成0111001的周期性脉冲序列,然后重复执行。脉冲序列在7个七个脉冲后重复。因此,需要-7计数器。 Mod-7计数器的输出将连接到解码器电路。为此,将设计一个mod –7计数器。需要进行三个T翻转(因为我们需要计数至000到110,因此需要3位)。

有关Mod — N计数器的设计,请参阅本文。

Mod-7计数器的设计–

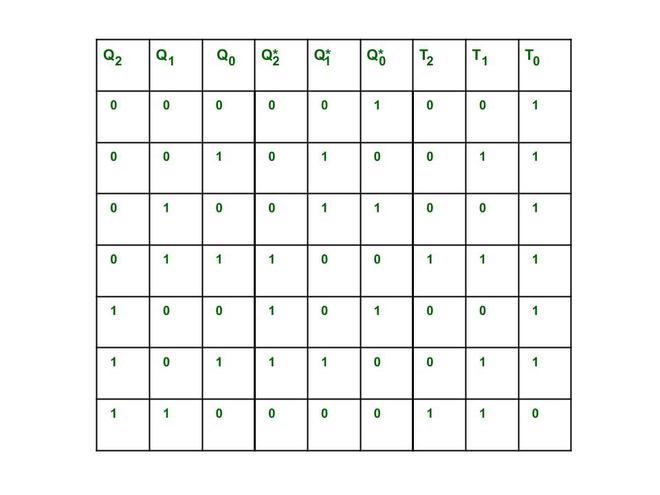

这里Q是先前状态,而Q *是下一个状态。

Mod-7计数器的电路励磁表

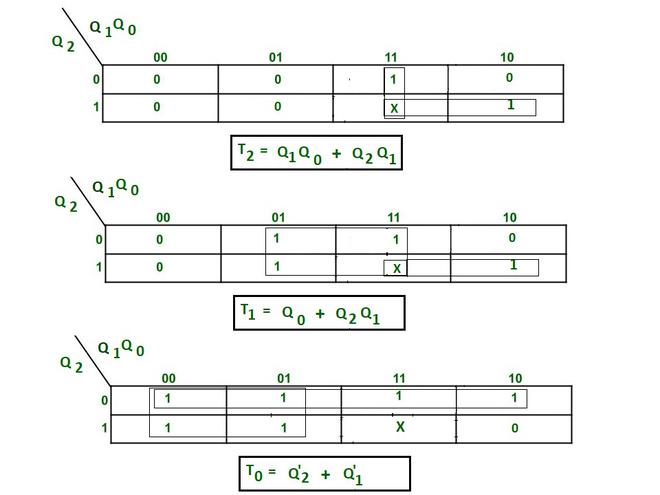

从K –映射获得的T型触发器的输入表达式如下所示。

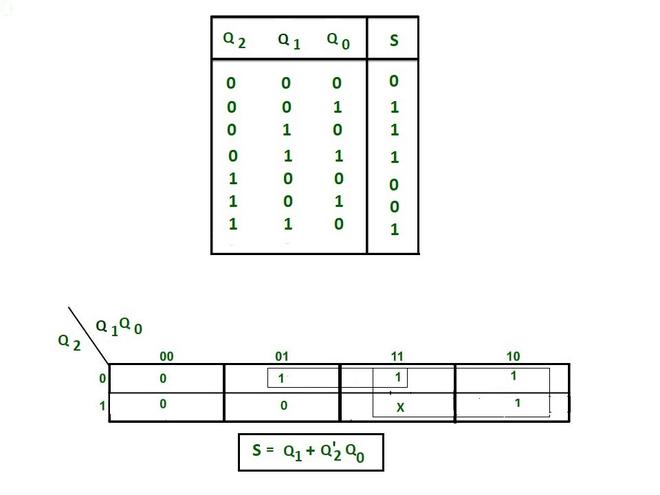

通过观察给定的时序序列获得解码器的真值表(0111001)。使用K图获得解码器的输出S的简化表达式。未使用的计数被视为无关。

每个计数序列都映射到一个控制信号位。

解码器的组合逻辑可以通过求解K映射来找到。

用于解码器电路的简化表达式为S = Q 1 + Q” 2 Q 0。

示例—当我们处于状态Q 2 = 0 Q 1 = 0 Q 0 = 0时,则S的值= 0 + 0.1 = 0。

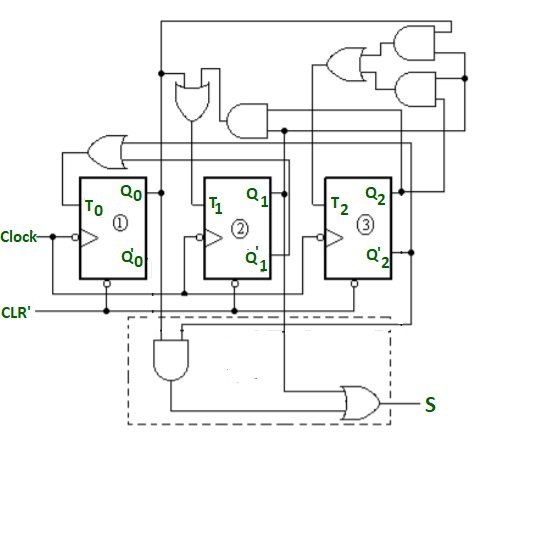

带有解码器的完整逻辑图。

解码器电路在每个时钟(-ve沿触发)脉冲之后生成输出。输出即S将作为其他电路的控制信号。

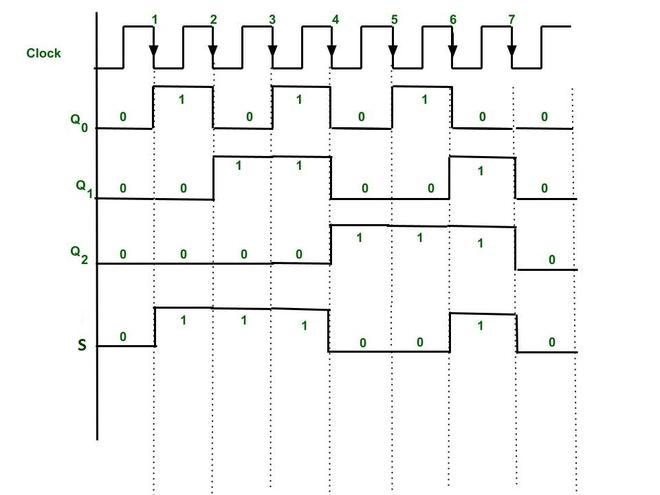

在每个负边缘时钟之后发生控制信号的产生,并且如下图所示,也可以绘制该控制信号的时序图。每个计数器状态用于产生一个控制信号。

通过计数器生成控制信号S的时序图