触发器是众所周知的基本数字存储电路。它具有两个状态,分别为逻辑1(高)和逻辑0(低)状态。触发器是一种时序电路,由信息或数据的单个二进制状态组成。该数字电路是一个触发器,具有两个输出并且处于相反的状态。它也被称为双稳态多谐振荡器。

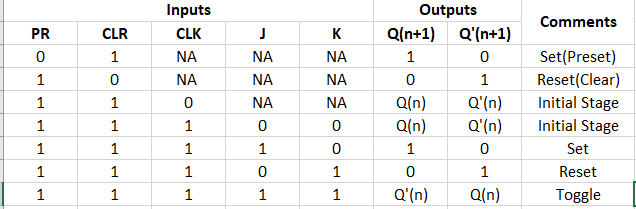

1. JK触发器:

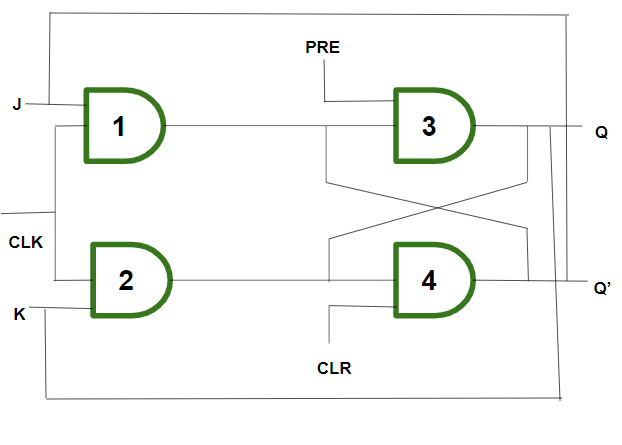

下面的JK触发器图表示基本结构,该结构由时钟(CLK),清除(CLR)和预设(PR)组成。

JK触发器中的操作–

- 情况1:

PR = CLR = 0此条件处于无效状态。

- 情况2:

PR = 0 and CLR = 1PR被激活,这意味着Q中的输出被设置为1。因此,触发器处于设置状态。

- 情况3:

PR = 1 and CLR = 0CLR被激活,这意味着Q’中的输出被设置为1。因此,触发器处于复位状态。

- 情况4:

PR = CLR = 1在这种情况下,触发器以其正常方式工作,而PR和CLR被禁用。

具有预设和清除功能的JK触发器–

JK触发器真相表–

JK触发器中的比赛条件-

当J和K都设置为1时,输入将保持高电平一段较长的时间,然后输出将继续切换。切换意味着立即切换输出,即Q = 0,Q’= 1将立即变为Q = 1和Q’= 0,并且这种连续性一直在变化。输出的这种变化会导致出现竞速情况。

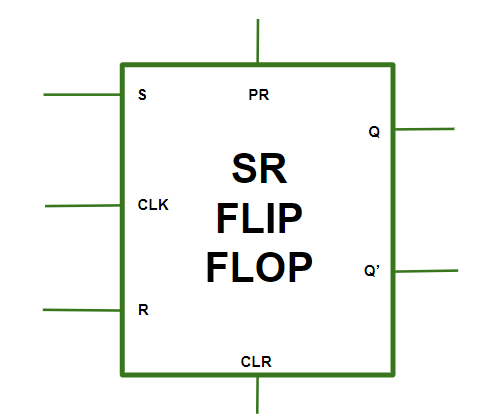

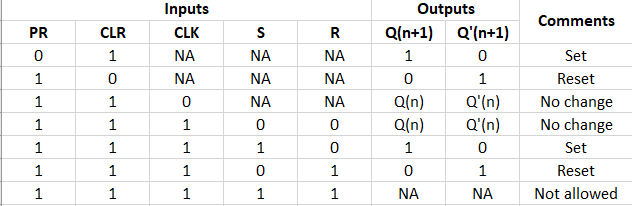

2. SR触发器:

在SR触发器中,借助“预设”和“清除”,在接通电源时,电路的状态会不断变化,即不确定。它可能进入置位(Q = 1)或复位(Q’= 0)状态。在许多应用中,希望首先置位或复位触发器。这是通过预设(PR)和清除(CLR)完成的。

SR触发器中的操作–

- 情况1:

PR = CLR = 1异步输入无效,触发器以正常方式自由响应S,R和CLK输入。

- 情况2:

PR = 0 and CLR = 1当Q设置为1时使用。

- 情况3:

PR = 1 and CLR = 0当Q’设置为1时使用。

- 情况4:

PR = CLR = 0这是无效状态。

SR触发器,带有“预设”和“清除”的表示形式–

SR触发器真值表–

触发器的应用:

- 触发器用作反弹消除开关。

- 它们用作串行到并行和并行到串行的转换。

- 它用于计数器。

- 它用于分频器,也可用作锁存器。