- JK触发器到T触发器的转换

- JK触发器到T触发器的转换

- JK触发器到D触发器的转换(1)

- JK触发器到T触发器的转换(1)

- JK触发器到D触发器的转换

- JK触发器到D触发器的转换

- JK触发器和SR触发器(1)

- JK触发器和SR触发器

- Verilog | JK触发器(1)

- Verilog | JK触发器

- jk (1)

- 主从 JK 触发器

- 主从 JK 触发器(1)

- jk - 任何代码示例

- JK触发器|计算机组织和架构教程

- JK触发器|计算机组织和架构教程(1)

- 数字电子领域的主从JK触发器(1)

- 数字电子领域的主从JK触发器

- jk canvas - Javascript 代码示例

- SQL |触发器

- 触发器 - SQL (1)

- SQL |触发器(1)

- MySQL触发器(1)

- MySQL触发器

- 触发器 - SQL 代码示例

- jquery 触发器 - Javascript (1)

- SR触发器到D触发器的转换(1)

- SR触发器到D触发器的转换

- SR触发器到T触发器的转换

📅 最后修改于: 2020-12-30 06:51:16 🧑 作者: Mango

JK人字拖

SR触发器或置位触发器具有很多优点。但是,它具有以下切换问题:

- 当设置“ S”和复位“ R”输入设置为0时,始终避免这种情况。

- 当设置或复位输入在启用输入为1时更改其状态时,将发生错误的闩锁动作。

JK触发器消除了SR触发器的两个缺点。

JK触发器是数字电路中最常用的触发器之一。 JK触发器是具有两个输入“ J”和“ K”的通用触发器。在SR触发器中,“ S”和“ R”是设置和复位的缩写缩写字母,但J和K不是。 J和K本身是自治字母,选择该字母可以将触发器设计与其他类型区分开。

JK触发器的工作方式与SR触发器的工作方式相同。 JK触发器具有“ J”和“ K”触发器,而不是“ S”和“ R”触发器。 JK触发器和SR触发器之间的唯一区别是,当SR触发器的两个输入都设置为1时,电路会产生无效状态作为输出,但是在JK触发器的情况下,即使两个触发器都没有无效状态“ J”和“ K”触发器设置为1。

JK触发器是带有时钟输入电路的门控SR触发器。当两个输入均设置为1时,将产生无效或非法输出条件,并通过添加时钟输入电路来防止这种情况发生。因此,JK触发器具有四个可能的输入组合,即1、0,“无变化”和“切换”。 JK触发器的符号与SR双稳态锁存器相同,只是增加了时钟输入。

框图:

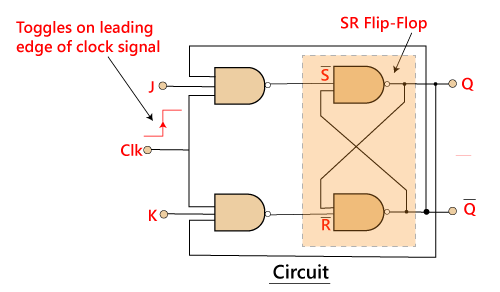

电路原理图:

在SR触发器中,输入“ S”和“ R”都被两个输入J和K代替。这意味着J和K输入分别等于S和R。

两个2输入与门被两个3输入与非门取代。每个门的第三个输入连接到Q和Q'的输出。 SR触发器的交叉耦合允许将先前无效的条件(S =“ 1”,R =“ 1”)用于产生“切换动作”,因为两个输入现已互锁。

如果电路是“置位”的,则J输入通过下级“与非”门从Q'的“ 0”位置中断。如果电路为“ RESET”,则通过上部NAND门从Q的0个位置中断K输入。由于Q和Q'总是不同的,因此我们可以使用它们来控制输入。当输入“ J”和“ K”都设置为1时,JK根据给定的真值表切换触发器。

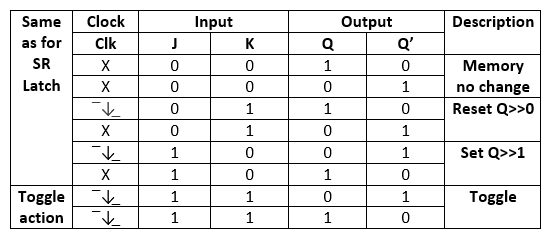

真相表:

当JK触发器的两个输入均设置为1且时钟输入也为脉冲“高”时,则从SET状态变为RESET状态,电路将被切换。当JK触发器的两个输入都设置为1时,它用作T型触发器。

JK触发器是一种改进的时钟SR触发器。但是它仍然遭受“种族”问题的困扰。当在时钟输入的定时脉冲有时间变为“关”之前改变输出Q的状态时,会发生此问题。为了避免这个时间段,我们必须保持较短的时间加上时间段(T)。