先决条件:硬接线控制单元

这里使用硬件生成控制信号。

共有三种类型的硬接线控制单元。

1 .状态表方法:

状态表法

- 这里控制单元的行为以表格的形式表示,称为状态表。

- 这里,每一行代表 T 状态,列代表指令。

- 特定列与每行的每个交点指示在指令的相应 T 状态中将产生哪个控制信号。

- 这里的硬件电路是为每一列(即特定指令)设计的,用于在不同的 T 状态下产生控制信号。

优势 –

- 这是最简单的方法。

- 该方法主要用于小型指令集处理器(即RISC处理器)。

缺点——

- 在现代处理器中,有非常多的指令集。因此,电路设计复杂,调试困难,如果我们对状态表进行任何修改,那么电路的大部分部分都需要更改。

- 因此,这并没有广泛用于这些类型的处理器。

- 电路设计中有很多冗余,例如获取指令所需的控制信号很常见,并且重复N条指令。因此电路设计的成本可能会增加。

2.延迟元素法:

- 这里控制单元的行为以流程图的形式表示。

- 流程图中的每一步都代表了一个需要为处理指令而产生的控制信号。

- 如果指令的所有步骤都执行完毕,则说明指令执行完毕。

- 控制信号执行微操作,每个微操作需要一个 T 状态。

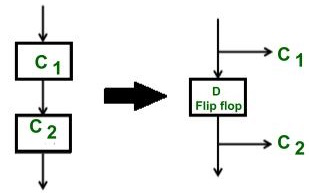

- 对于独立的微操作,需要在不同的T状态下进行。因此,对于每个连续的控制信号,都需要精确的 1 态延迟,这可以在 D FF 的帮助下产生。

- 所以。 D 触发器被插入在每两个连续的控制信号之间。

- 正如我们所观察到的,D FF 是在每对控制信号之间引入的。因此,在生成控制信号之后,直到下一条指令需要该控制信号之前,才会使用该控制信号之前的延迟元件。因此,在所有 D 触发器中,一次只有一个处于活动状态。因此,这种方法也被称为一热法。

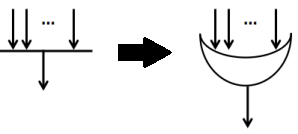

- 在流程图中,如果控制信号有多个入口点,那么为了组合两条或更多条路径,我们使用或门。

- 一个决策框被转换成一组两个互补的与门。

例子 –

假设处理器有两条指令加法或减法(因此需要1位的操作码,其中0操作码用于加法指令,1操作码用于减法。

用于产生控制信号的延迟元件方法。

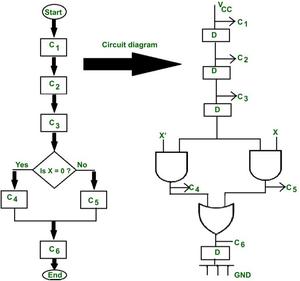

流程图设计——

说 C 1 ,C 2 ,C 3是取指令的控制信号。当X=0时,产生C 4控制信号(即译码),用于进行加法运算,当x=1时,产生控制信号C 5进行减法运算。并且c 6控制信号用于存储结果并且过程结束。

电路设计——

在两个独立的连续控制信号之间,在它们之间引入一个延迟元件以产生1T状态的延迟。决策框被转换为互补的与门电路(即如果x= 0则x’= 1,因此,产生ac 4控制信号。

优势 –

- 这种方法具有逻辑性,因此有助于降低电路复杂度。

- 对于每条指令都需要产生的公共控制信号,只能设计一个电路。

缺点——

- 随着指令数量的增加,用于产生延迟的D FF的数量也增加,因此整体电路复杂度和成本增加。

3. 序列计数器法:

序列计数器方法

- 这是在每个连续控制信号之间产生延迟的最流行和最常用的方法。

它的主要优点是它使用流程图的逻辑方法,并且不使用不必要的 D FF 数量。 - 首先,流程图旨在表示控制单元的行为。

- 然后使用与与或门相同的方法将其转换为电路(如上面的延迟元素方法中所见)。

延迟元素方法中使用的 2 条指令示例

延迟元素方法中使用的2条指令示例[/caption]

- 它类似于延迟元件方法,但唯一的区别是电路中没有不必要的D触发器,而是有触发点。它们在一对一的 T 状态间隙后被激活。

序列计数器电路的工作 –

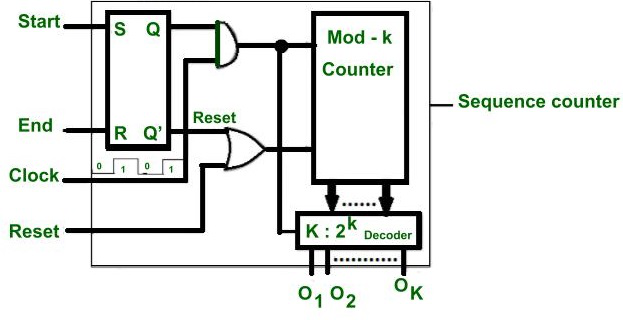

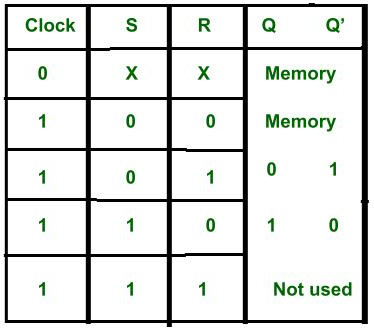

- 这里使用了一个 SR FF 、一个解码器和一个计数器。

SR FF真值表

- 当指令周期开始时,则 start = 1 。

- 我们知道,当 Start = 1 时,因为 S 连接到 Start,因此 Q 变为 1,Q’ 变为 0。

- 这里使用电平触发时钟。因此,当clock = 1或高且Start = 1时,由于两个输出都连接到AND门,因此如果两者的结果都是1,则将使能计数器并且计数器从0 0 0状态开始计数。因此0 0 0 状态被解码器解码并产生输出O 1 ,这将触发控制电路中的触发点。

- 随着时钟在 1 T 状态后再次变高。因此,当时钟 = 0 时,计数器状态将保持不变(Q 和 Q’)直到时钟再次变为高电平。这确保计数器在一对一的 T 状态间隔后改变其状态。

- 假设计数器是 3 位,它生成 2 3 = 8 个状态(000 001 ….. 111) 。第一个计数 0 0 0 被提供给 3:8 解码器。它将激活 1 号输出。该输出不是控制信号,但会触发控制单元电路中的触发点。

- 由于时钟在一个 T 状态的间隙后再次变高,因此时钟 =1 且开始 = 1,然后计数器被启用并将其状态更改为 001,计数器解码计数并使 O 2输出高电平。这将触发电路中的第二个触发点。

- 所有计数状态都以相同的方式解码。

如果计数器为 K 位,则需要 K:2 K解码器,这可以产生 2K 输出,并在电路中出现 1-1 个 T 状态间隙后触发 2K 触发点。

- 当指令结束时,产生控制信号使End pin = 1,计数器复位,所以下一次,从第一个count(0 0 0 )开始。

- 如果复位引脚 =1,则计数器将复位,之后它将再次从 000 状态开始计数。

优点:

- 使用较少数量的触发器。

硬接线控制单元的缺点:

- 在现代处理器中,有非常多的指令集。因此,电路设计复杂,调试困难,如果我们进行任何修改,则需要更改很大一部分电路。因此,它适用于 RISC 处理器。