触发器可用于存储一位二进制数据(1 或 0)。但是,为了存储多位数据,我们需要多个触发器。 N 个触发器按顺序连接以存储 n 位数据。寄存器是用于存储此类信息的设备。它是一组串联的触发器,用于存储多位数据。

存储在这些寄存器中的信息可以借助移位寄存器进行传输。移位寄存器是一组用于存储多位数据的触发器。通过施加时钟脉冲,可以使存储在此类寄存器中的位在寄存器内移动和移入/移出寄存器。通过连接 n 个触发器可以形成一个 n 位移位寄存器,其中每个触发器存储一位数据。

将位左移的寄存器称为“左移寄存器”。

将位右移的寄存器称为“右移寄存器”。

移位寄存器基本上有 4 种类型。这些是:

- 串行输入串行输出移位寄存器

- 串行输入并行输出移位寄存器

- 并行输入串行输出移位寄存器

- 并行输入并行输出移位寄存器

串行输入串行输出移位寄存器 (SISO) –

允许串行输入(通过单个数据线一位接一位)并产生串行输出的移位寄存器称为串行输入串行输出移位寄存器。由于只有一个输出,数据以串行模式一次一位地离开移位寄存器,因此名称为串行输入串行输出移位寄存器。

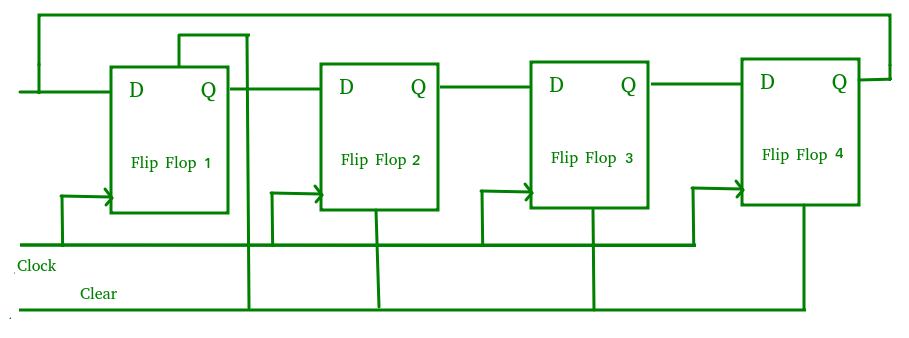

下面给出的逻辑电路显示了一个串行输入串行输出移位寄存器。该电路由四个串联的D触发器组成。所有这些触发器彼此同步,因为相同的时钟信号应用于每个触发器。

上面的电路是一个右移寄存器的例子,从触发器的左侧取串行数据输入。 SISO 的主要用途是充当延迟元件。

串行输入并行输出移位寄存器 (SIPO) –

允许串行输入(通过单个数据线一位接一位)并产生并行输出的移位寄存器称为串行输入并行输出移位寄存器。

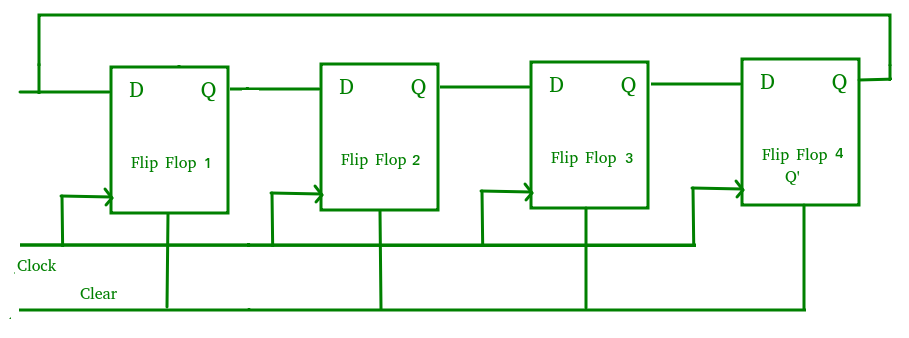

下面给出的逻辑电路显示了一个串行输入并行输出移位寄存器。该电路由四个相连的D触发器组成。除时钟信号外,清除 (CLR) 信号还连接到所有 4 个触发器,以便复位它们。第一个触发器的输出连接到下一个触发器的输入,依此类推。所有这些触发器彼此同步,因为相同的时钟信号应用于每个触发器。

上面的电路是一个右移寄存器的例子,从触发器的左侧获取串行数据输入并产生并行输出。它们用于需要将一条数据线多路分解为多条并行线的通信线路,因为 SIPO 寄存器的主要用途是将串行数据转换为并行数据。

并行输入串行输出移位寄存器 (PISO) –

允许并行输入(数据分别以同时方式提供给每个触发器)并产生串行输出的移位寄存器称为并行输入串行输出移位寄存器。

下面给出的逻辑电路显示了并行输入串行输出移位寄存器。该电路由四个相连的D触发器组成。时钟输入直接连接到所有触发器,但输入数据通过每个触发器输入端的多路复用器单独连接到每个触发器。前一个触发器的输出和并行数据输入连接到 MUX 的输入,MUX 的输出连接到下一个触发器。所有这些触发器彼此同步,因为相同的时钟信号应用于每个触发器。

并行输入串行输出 (PISO) 移位寄存器用于将并行数据转换为串行数据。

并行输入并行输出移位寄存器 (PIPO) –

允许并行输入(数据分别以同时方式提供给每个触发器)并产生并行输出的移位寄存器称为并行输入并行输出移位寄存器。

下面给出的逻辑电路显示了并行输入并行输出移位寄存器。该电路由四个相连的D触发器组成。清除 (CLR) 信号和时钟信号连接到所有 4 个触发器。在这种类型的寄存器中,由于不需要数据的串行移位,因此各个触发器之间没有互连。数据作为每个触发器的输入单独给出,并且以相同的方式,输出也从每个触发器单独收集。

并行输入并行输出 (PIPO) 移位寄存器用作临时存储设备,与 SISO 移位寄存器一样,它充当延迟元件。

双向移位寄存器 –

如果我们将一个二进制数向左移一位,相当于将这个数乘以 2;如果我们将一个二进制数向右移一位,则相当于将这个数除以 2。执行这些操作我们需要一个可以在任一方向移动数据的寄存器。

双向移位寄存器是能够根据所选模式向右或向左移位数据的寄存器。如果选择的模式为 1(高),则数据将向右移动,如果选择的模式为 0(低),则数据将向左移动。

下面给出的逻辑电路显示了一个双向移位寄存器。该电路由四个相连的D触发器组成。输入数据连接在电路的两端,根据选择的模式,只有一个和门处于活动状态。

移位寄存器计数器 –

移位寄存器计数器是将输出连接回输入以产生特定序列的移位寄存器。这些基本上分为两种类型:

- 环形计数器 –

环形计数器基本上是一个移位寄存器计数器,其中第一个触发器的输出连接到下一个触发器,依此类推,最后一个触发器的输出再次反馈到第一个触发器的输入,因此名戒柜台。只要施加时钟脉冲,移位寄存器内的数据模式就会循环。

下面给出的逻辑电路显示了一个环形计数器。该电路由四个相连的D触发器组成。由于电路由四个触发器组成,因此数据模式将在每四个时钟脉冲后重复一次,如下面的真值表所示:

通常使用环形计数器,因为它是自解码的。不需要额外的解码电路来确定计数器处于什么状态。

- 约翰逊柜台 –

约翰逊计数器基本上是一个移位寄存器计数器,其中第一个触发器的输出连接到下一个触发器,依此类推,最后一个触发器的反相输出再次反馈到第一个触发器的输入。它们也被称为扭环计数器。下面给出的逻辑电路显示了约翰逊计数器。该电路由四个相连的D触发器组成。 n 级约翰逊计数器产生 2n 个不同状态的计数序列,因此也称为 mod-2n 计数器。由于电路由四个触发器组成,因此数据模式将每八个时钟脉冲重复一次,如下面的真值表所示:

约翰逊计数器的主要优点是与环形计数器相比,它只需要 n 个触发器来循环给定数据以生成 2n 个状态的序列。

移位寄存器的应用——

- 移位寄存器用于临时数据存储。

- 移位寄存器也用于数据传输和数据操作。

- 串行输入串行输出和并行输入并行输出移位寄存器用于对数字电路产生时间延迟。

- 串行输入并行输出移位寄存器用于将串行数据转换为并行数据,因此它们用于需要将一条数据线解复用为多条并行线的通信线路中。

- 并行输入串行输出移位寄存器用于将并行数据转换为串行数据。

参考 –

注册 – ee.usyd.edu.au