- 数字电子产品中的寄存器

- 数字电子产品中的寄存器(1)

- 计算机寄存器(1)

- 计算机寄存器

- c#寄存器写入值 - C#(1)

- Vim-寄存器

- Vim-寄存器(1)

- 二进制寄存器数据

- c#寄存器写入值 - C#代码示例

- 数字逻辑中的移位寄存器(1)

- 数字逻辑中的移位寄存器

- 汇编-寄存器

- 汇编-寄存器(1)

- 寄存器模式和寄存器间接模式的区别(1)

- 寄存器模式和寄存器间接模式的区别

- 寄存器模式和寄存器间接模式的区别

- 寄存器模式和寄存器间接模式的区别(1)

- 数字电子中的移位寄存器(1)

- 数字电子中的移位寄存器

- 寄存器模式和寄存器间接模式之间的区别(1)

- 寄存器模式和寄存器间接模式之间的区别

- 寄存器和内存的区别(1)

- 寄存器和内存的区别

- 寄存器和内存的区别(1)

- 寄存器和内存的区别

- 8085程序,用于访问并与寄存器B交换标志寄存器的内容(1)

- 8085程序,用于访问并与寄存器B交换标志寄存器的内容

- 寄存器和缓冲区的区别

- 寄存器和缓冲区的区别

📅 最后修改于: 2021-01-12 04:56:13 🧑 作者: Mango

触发器是一个1位存储单元,可用于存储数字数据。为了增加位数的存储容量,我们必须使用一组触发器。这样的一组触发器被称为寄存器。 n位寄存器将由n个触发器组成,并且能够存储n位字。

寄存器中的二进制数据可以在寄存器内从一个触发器移动到另一个触发器。允许这种数据传输的寄存器称为移位寄存器。移位寄存器有四种操作模式。

- 串行输入串行输出

- 串行输入并行输出

- 并行输入串行输出

- 并行输入并行输出

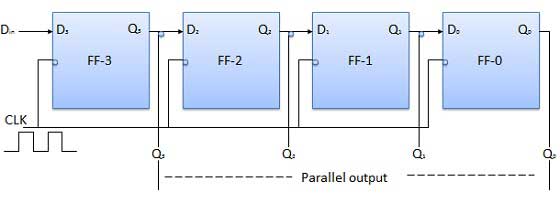

串行输入串行输出

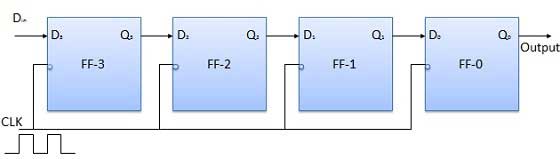

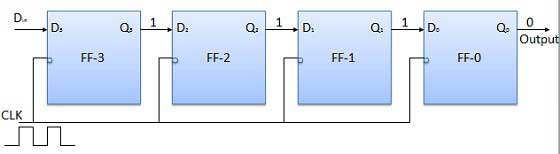

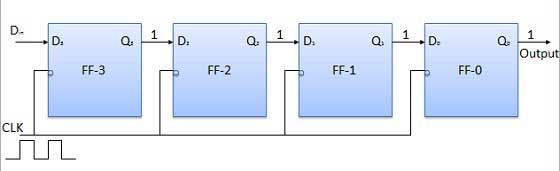

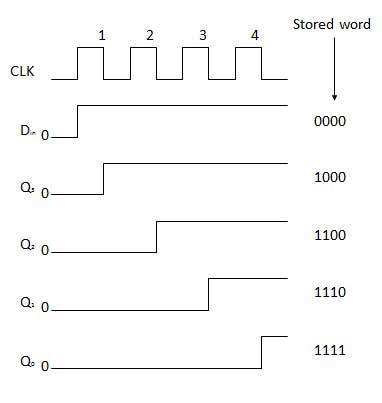

让所有触发器最初处于复位状态,即Q 3 = Q 2 = Q 1 = Q 0 =0。如果将四位二进制数1 1 1 1输入到寄存器,则该数字应为施加到d中的位与施加第一LSB比特。 FF-3的D输入(即D 3 )连接到串行数据输入D in 。 FF-3的输出(即Q 3 )连接到下一个触发器的输入(即D 2) ,依此类推。

框图

操作方式

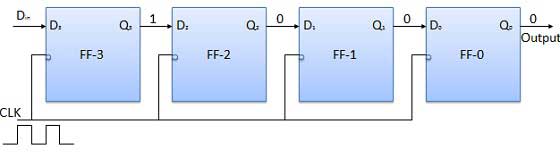

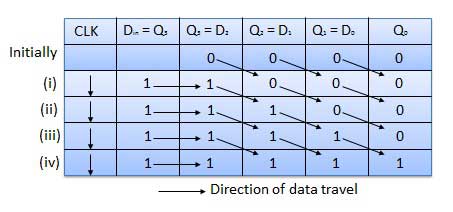

在施加时钟信号之前,让Q 3 Q 2 Q 1 Q 0 = 0000并将要输入的数字的LSB位施加到D in中。因此D in = D 3 =1。施加时钟。在时钟的第一个下降沿,FF-3被置1,寄存器中存储的字为Q 3 Q 2 Q 1 Q 0 = 1000。

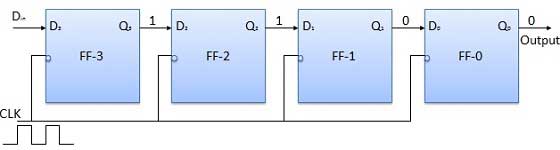

将下一位应用于D中的D。因此D in =1。一旦时钟的下一个下降沿触发,FF-2将置1,存储的字变为Q 3 Q 2 Q 1 Q 0 = 1100。

应用下一个要存储的位,即1到D in 。施加时钟脉冲。一旦第三个负时钟边沿触发,将设置FF-1,并将输出修改为Q 3 Q 2 Q 1 Q 0 = 1110。

类似地,当D in = 1且到达第四个负时钟沿时,寄存器中存储的字为Q 3 Q 2 Q 1 Q 0 = 1111。

真相表

波形图

串行输入并行输出

-

在这种类型的操作中,数据被串行输入并以并行方式取出。

-

数据一点一点地加载。只要数据正在加载,输出就被禁用。

-

一旦数据加载完成,所有触发器都包含其所需的数据,则启用输出,以便可以同时在所有输出线上使用所有加载的数据。

-

加载一个四位字需要4个时钟周期。因此,SIPO模式的运行速度与SISO模式相同。

框图

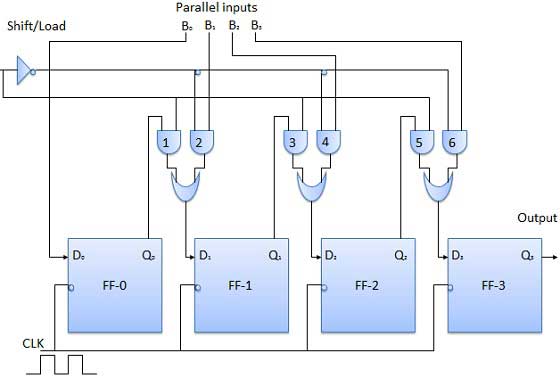

并行输入串行输出(PISO)

-

数据位以并行方式输入。

-

下面显示的电路是一个四位并行输入串行输出寄存器。

-

前一个触发器的输出通过组合电路连接到下一个触发器的输入。

-

二进制输入字B 0 ,B 1 ,B 2 ,B 3通过相同的组合电路施加。

-

该电路可以在两种模式下工作-换档模式或负载模式。

加载方式

当移位/负载条线为低(0)时,与门2、4和6变为活动状态,它们会将B 1 ,B 2 ,B 3位传递给相应的触发器。在时钟的下降沿,二进制输入B 0 ,B 1 ,B 2 ,B 3将被加载到相应的触发器中。因此发生平行加载。

换档模式

当变速/负载条线为低(1)时,与门2、4和6变为无效。因此,并行加载数据变得不可能。但是与门1,3和5变为活动状态。因此,在施加时钟脉冲时,数据从左向右逐位移位。因此发生并行输入串行输出操作。

框图

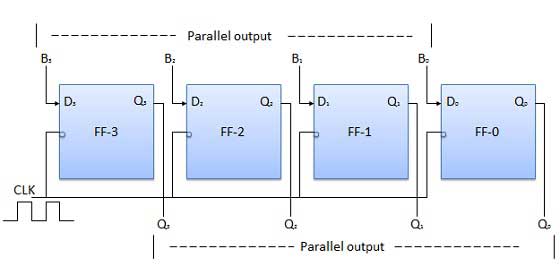

并行输入并行输出(PIPO)

在该模式下,将4位二进制输入B 0 ,B 1 ,B 2 ,B 3分别施加到四个触发器的数据输入D 0 ,D 1 ,D 2 ,D 3 。一旦施加了负时钟沿,输入的二进制位将同时加载到触发器中。加载的位将同时出现在输出侧。只有时钟脉冲对于加载所有位至关重要。

框图

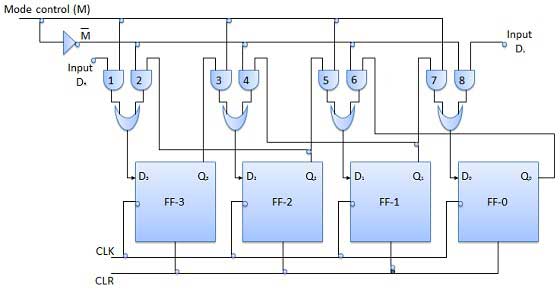

双向移位寄存器

-

如果将二进制数左移一位,则等于将原始数乘以2。类似地,如果将二进制数右移一位,则等同于将原始数除以2。

-

因此,如果我们要使用移位寄存器对给定的二进制数进行乘法和除法运算,则应该能够向左或向右移动数据。

-

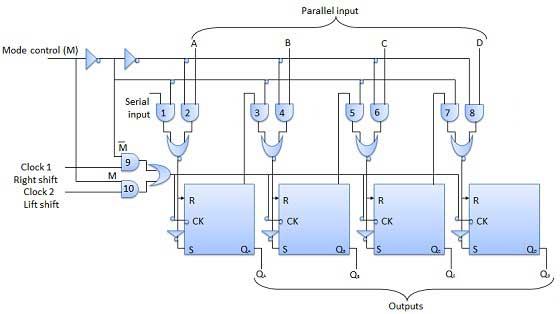

这种寄存器称为双向寄存器。图4示出了一个四位双向移位寄存器。

-

有两个串行输入,即串行右移数据输入DR和串行左移数据输入DL以及模式选择输入(M)。

框图

操作方式

| S.N. | Condition | Operation |

|---|---|---|

| 1 | With M = 1 − Shift right operation |

If M = 1, then the AND gates 1, 3, 5 and 7 are enabled whereas the remaining AND gates 2, 4, 6 and 8 will be disabled. The data at DR is shifted to right bit by bit from FF-3 to FF-0 on the application of clock pulses. Thus with M = 1 we get the serial right shift operation. |

| 2 | With M = 0 − Shift left operation |

When the mode control M is connected to 0 then the AND gates 2, 4, 6 and 8 are enabled while 1, 3, 5 and 7 are disabled. The data at DL is shifted left bit by bit from FF-0 to FF-3 on the application of clock pulses. Thus with M = 0 we get the serial right shift operation. |

通用移位寄存器

只能在一个方向上移位数据的移位寄存器称为单向移位寄存器。可以在两个方向上移位数据的移位寄存器称为双向移位寄存器。采用相同的逻辑,可以在两个方向上移位数据并并行加载数据的移位寄存器被称为通用移位寄存器。移位寄存器能够执行以下操作-

- 平行加载

- 左移

- 右移

模式控制输入连接到逻辑1进行并行加载操作,而连接到0进行串行移位。模式控制引脚接地时,通用移位寄存器用作双向寄存器。对于串行左操作,该输入将应用于串行输入,该串行输入将进入如图所示的AND门1。对于右移操作,串行输入应用于D输入。

框图