先决条件:波纹计数器。

在异步/纹波计数器中,第一个触发器的输出被提供为第二个触发器的时钟,即触发器(FF)不是同时计时的。

电路更简单,但速度慢。

异步计数器基础:

1 位异步/纹波计数器

当施加-ve 边沿时钟脉冲并将输入提供给FF 逻辑1 时,FF 的输出状态将在每个下降沿切换。输出频率将为 f/2(如果 f 是时钟频率)。它被称为二进制或 mod -2 计数器或位纹波计数器。

它有 2 个独特的输出状态(0 和 1)。

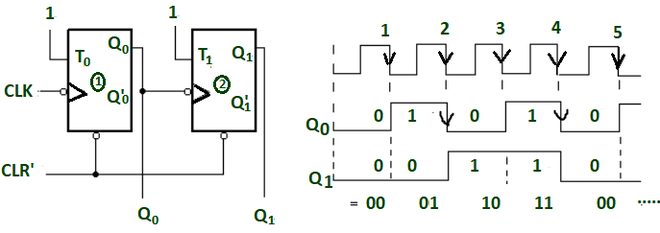

2 位异步递增计数器。

当两个 FF 串联并且一个 FF 的输出作为第二个 FF 的时钟时。因此,仅当输出和第一个 FF 为逻辑 1 且出现下降沿时,第二个 FF 的状态才会改变。 Q 1的输出频率为 f/4(如果 f 是时钟频率)。

它可以生成 4 种不同的独特状态。这称为除以 4 电路或 mod 4 纹波计数器。

此处输出为 Q 1 (MSB) Q 0 (LSB)。

由此,我们可以得出结论——

如果有 n 个 FF,则输出频率将除以 2 n 。还生成 2n 个唯一状态。

所以分频基本形成计数状态。

在这里,我们看到第一个 FF 的输出充当第二个 FF 的时钟。假设 FF 需要 30ns 来生成输出(即由于门的传播延迟)。因此,将在 60 ns 后获得第二个 FF 的输出。因此,传播延迟是通过 FF 的涟漪,并且随着 FF 数量的增加而变得更多。

因此,异步计数器对于产生大计数来说太慢了。

- 正如我们所知,当前一个 FF 的输出状态(即 Q )作为时钟提供给下一个 FF 时,计数器将执行如上所示的向上计数(即 0 1 2 3)。

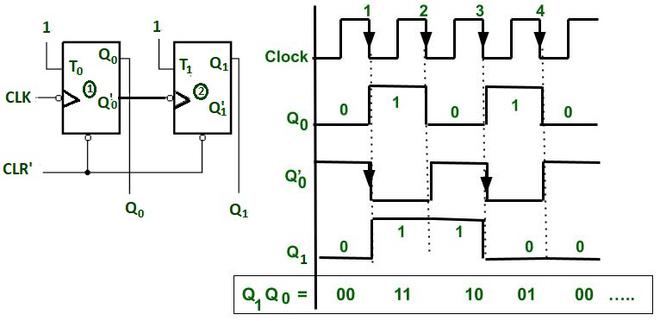

在第 4 个边沿时钟脉冲之后,序列将重复。 - 当前一个 FF 的互补输出状态(即Q’ )作为时钟提供给下一个 FF 时,计数器将执行向下计数,如下所示(即 3 2 1 0)。

在第 4 个边沿时钟脉冲之后,序列将重复。

2位异步递减计数器

现在我们正在设计加/减计数器。

向上/向下计数器是两个计数器的组合,我们可以通过更改模式控制输入来执行向上或向下计数。

3位异步递增/递减计数器的设计:

它不仅仅用于单独的向上或向下计数器。

- 在这种情况下,模式控制输入(比如 M)用于选择向上和向下模式。

- 每对触发器之间需要一个组合电路来决定是向上计数还是向下计数。

对于 n = 3,即对于 3 位计数器 –

最大计数 = 2 n -1并且状态数为2 n 。

设计涉及的步骤是:

步骤 1 :模式控制输入的决定 –

模式控制输入的决定

当 M = 0 时,则 Y = Q,因此它将执行向上计数(如上所述)。

当 M = 1 时,则 Y = Q’ 因此它将执行向下计数(如上所述)。

决定模式控制(即计数器是向上计数还是向下计数)需要组合电路。

所以所有可能的组合是——

K-map 用于查找将作为时钟提供给下一个 FF 的输出 Y。

寻找Y的K图

第 2 步:在每对 FF 之间插入组合逻辑 –

加/减计数器

时序图:

最初 Q 3 = 0,Q 2 = 0,Q 1 = 0。

3位异步递增/递减计数器时序图

情况 1 –当 M=0 时,则 M’ =1。

将其放入 Y = M’Q + MQ’= Q所以 Q 充当下一个 FF 的时钟。

因此,计数器将充当向上计数器。

向上计数器的说明 –

- 第一个 FF 连接到逻辑 1。因此,它会在每个下降沿触发。

- 第二个 FF 输入连接到 Q 1 。因此,当 Q 1 = 1 并且有时钟下降沿时,它会改变其状态。

- 类似地,第三个FF连接到Q 2 。因此,当 Q 2 = 1 且有时钟下降沿时,它会改变其状态。

- 通过这个我们可以生成向上计数器的计数状态。

- 在每 8 个下降沿之后,计数器再次达到状态 0 0 0。

因此,它也被称为除以 8 电路或模 8 计数器。

情况 2 –当 M=1 时,则 M’ =0。

把它放在Y= M’Q + MQ’= Q’ 中。所以 Q’ 充当下一个 FF 的时钟。

因此,计数器将充当向下计数器。

向下计数器的说明 –

- 第一个 FF 连接到逻辑 1。因此,它会在每个下降沿触发。

- 第二个 FF 输入连接到 Q’ 1 。因此,当 Q’ 1 = 1 并且有时钟下降沿时,它会改变其状态。

- 类似地,第三个FF连接到Q’ 2 。因此,当 Q’ 2 = 1 且有时钟下降沿时,它会改变其状态。

- 通过这个我们可以生成递减计数器的计数状态。

- 在每 8 个下降沿之后,计数器再次达到状态 0 0 0。

因此,它也被称为除以 8 电路或模 8 计数器。