柜台 :

计数器用于对时钟脉冲进行计数。时钟脉冲以固定间隔出现。它们用于测量时间和频率。我们也可以说计数器是在时钟脉冲的帮助下改变其预定义状态的时序电路。它们由触发器和逻辑门构成。

它们有两种类型——

- 异步计数器

- 同步计数器

在异步计数器中,只为第一个触发器提供外部时钟脉冲,此后第一个 FF 的输出用作第二个 FF 的时钟脉冲,依此类推。在同步 FF 的情况下,所有触发器都由外部时钟脉冲同时触发。

请参阅此,以了解异步计数器的工作原理。

3位异步递减计数器:

- 对于 3 位计数器,我们需要 3 个触发器,我们可以生成 2 3 = 8 个状态和计数(111 110 … 000)。

- 我们可以通过两种方式在异步递减计数器中生成递减计数状态。

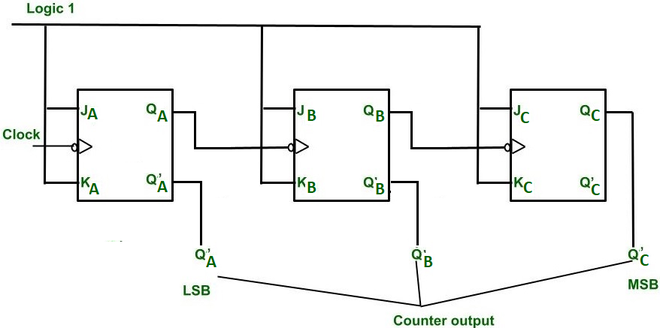

方法一:

在此实现中,时钟脉冲(占空比为 50%)仅提供给第一个 FF。此后,第一个FF的输出作为时钟提供给第二个FF,第二个FF的输出作为第三个FF的时钟提供。但是互补的输出是从每个 FF 中获取的(即与向上计数器相同,但输出状态是互补的)。这里 Q A是 LSB,Q C是 MSB。

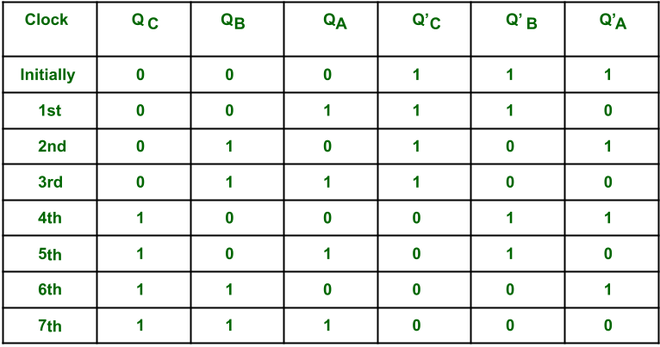

状态表——

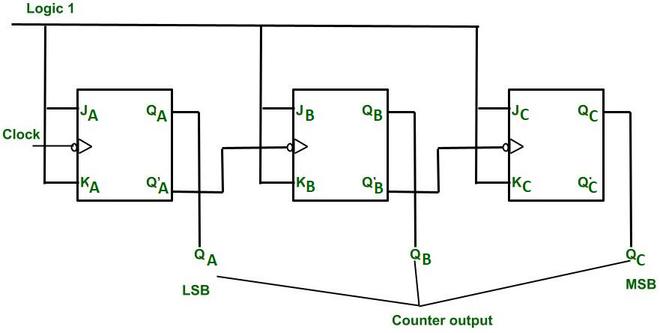

方法二:

在这个实现中,时钟脉冲只提供给第一个 FF。此后,第一个FF(Q’ A )的互补输出作为时钟馈送到第二FF,并且第二FF的互补输出(即Q’ B )作为第三FF的时钟馈送。但是输出(Q)取自每个FF。

通过这两种实现,我们可以获得相同的计数状态。

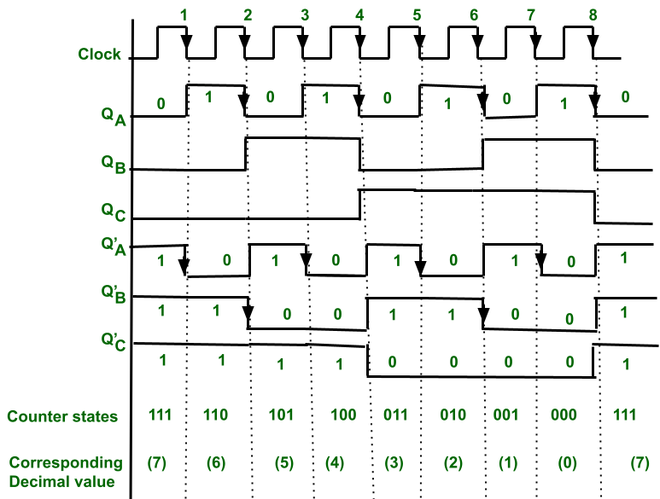

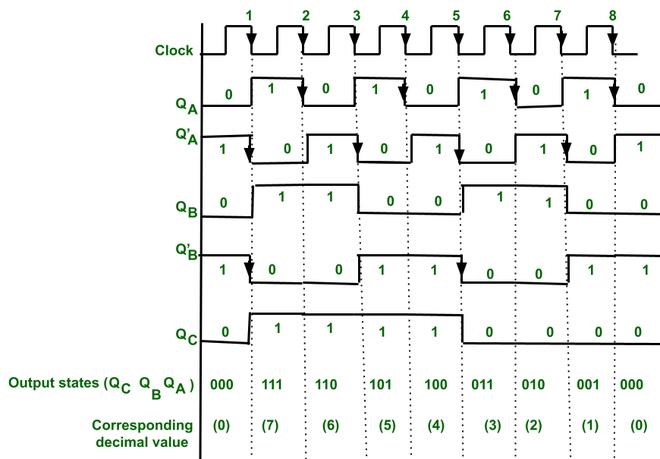

时序图 –

通过时序图可以很容易地理解计数器的工作。

解释 –

- 这里使用了-ve 边沿时钟脉冲(即计数器状态转换只能发生在时钟脉冲的下降沿),因此将发生翻转。

- 所有的计数器状态都是由分频产生的。

- 最初 Q A =0 Q B =0 且 Q C = 0。

第一回路——

- -ve 边沿时钟脉冲提供给第一个计数器。因此,第一个计数器的输出状态(即 Q A )将在时钟脉冲的每个下降沿触发。

- 由于 Q A作为时钟馈送到第二个 FF,因此输出状态(即 Q B )将在 Q A 的每个下降沿触发。

- 同样,Q B作为第三个 FF 的时钟,因此第三个 FF 的输出状态 (Q C ) 将在 Q B 的每个下降沿触发。

- 我们知道,这是 UP 计数器的工作,但这里的输出采用补码形式(即 Q’ C Q’ B Q’ A ),因此我们得到补码输出(即向下计数 111 到 000)

- 在外部时钟脉冲的第 8 个下降沿后,计数器复位为 000。

第一个电路的时序图

第二回路——

- -ve 边沿时钟脉冲提供给第一个计数器。因此,第一个计数器的输出状态(即 Q A )将在时钟脉冲的每个下降沿触发。

- 由于互补输出(Q’ A )作为时钟馈送到第二个FF,因此输出状态(即Q B )将在Q’ A 的每个下降沿切换。

- 以同样的方式,Q’B 作为第三个 FF 的时钟,因此第三个 FF 的输出状态 (Q C ) 将在 Q’ B 的每个下降沿触发。

- 在这种情况下,三个FF的输出被视为(Q C Q B Q A )。

- 在外部时钟脉冲的第 8 个下降沿后,计数器复位为 000。

- 这里,可以在第一个边沿时钟脉冲之后(即在第一个脉冲之后计数输出变为111)获得向下计数状态。

第二电路的时序图

异步计数器的优点:

- 由于传播延迟的累积,它们用于低速电路。

- 它们易于设计。

- 它们用于 mod n 计数器,以及将输入除以 n 的除以 n 计数器(即 n 是整数)。

异步计数器的缺点:

- 随着触发器数量的增加,传播延迟也会增加。

- 对于高时钟频率,由于传播延迟可能会出现计数错误。

例如

由于传播延迟导致的错误计数状态

由于传播延迟(通过计数器),切换动作发生在一些延迟之后,因此可能会产生错误的计数状态。

- 在截断计数器的情况下(即在 mod 计数器中),需要额外的反馈逻辑(即逻辑门)。