- adc 程序集 (1)

- adc 程序集 - 任何代码示例

- 间接型ADC(1)

- 间接型ADC

- 8086 中的 adc 指令 (1)

- 8086 中的 adc 指令 - 任何代码示例

- COMO ADC HOVER - CSS (1)

- COMO ADC HOVER - CSS 代码示例

- ADC 和数字输入引脚有什么区别? (1)

- 直接地址表

- 直接地址表(1)

- ADC 和数字输入引脚有什么区别? - 无论代码示例

- 应用程序交付控制器(ADC)概述

- 应用程序交付控制器(ADC)概述(1)

- 应用程序交付控制器(ADC)概述

- 应用程序交付控制器(ADC)概述(1)

- pic32 adc 轮询代码 (1)

- fs 方法直接 (1)

- pic32 adc 轮询代码 - 任何代码示例

- fs 方法直接 - 无论代码示例

- 直接为元素设置样式 - 无论代码示例

- 直接替代的限制(1)

- 直接替代的限制

- 如何直接从 GitHub 安装 npm 包?(1)

- 如何直接从 GitHub 安装 npm 包?

- 直接招聘流程

- 不安全的直接对象引用(1)

- 不安全的直接对象引用

- 如何在 R 中的 ggplot2 中直接添加标签(1)

📅 最后修改于: 2020-11-24 07:07:20 🧑 作者: Mango

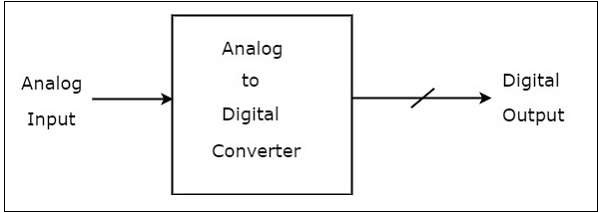

模数转换器(ADC)将模拟信号转换为数字信号。数字信号用二进制代码表示,该二进制代码是位0和1的组合。

ADC的框图如下图所示-

请注意,在上图中,模数转换器(ADC)由一个模拟输入和多个二进制输出组成。通常,ADC的二进制输出数量为2的幂。

ADC有两种类型:直接型ADC和间接型ADC。本章详细讨论直接型ADC。

如果ADC通过利用内部生成的等效数字(二进制)代码直接与模拟输入进行模数转换,则称为直接型ADC 。

以下是直接型ADC的示例–

- 计数器类型ADC

- 逐次逼近型ADC

- 闪存型ADC

本节详细讨论这些直接类型ADC。

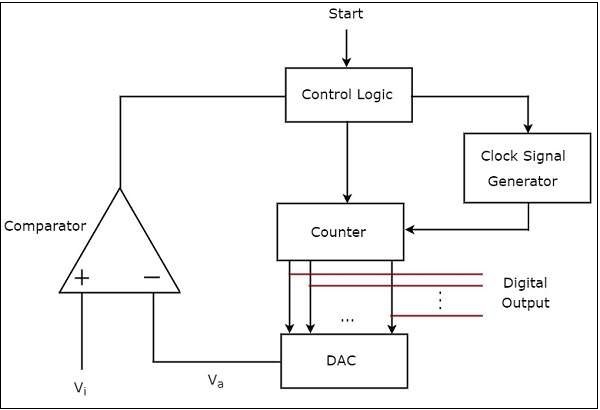

计数器类型ADC

计数器类型的ADC通过内部使用计数器操作来产生数字输出,该数字输出近似等于模拟输入。

下图显示了计数器类型ADC的框图–

计数器型ADC主要由5个模块组成:时钟信号发生器,计数器,DAC,比较器和控制逻辑。

计数器类型ADC的工作如下-

-

当控制逻辑接收到启动命令信号时,它会复位计数器并启用时钟信号发生器,以便将时钟脉冲发送到计数器。

-

对于每个时钟脉冲,计数器将增加一,其值将采用二进制(数字)格式。计数器的此输出用作DAC的输入。

-

DAC将接收到的二进制(数字)输入(即计数器的输出)转换为模拟输出。比较器将此模拟值$ V_ {a} $与外部模拟输入值$ V_ {i} $进行比较。

-

只要than大于,比较器的输出将为“ 1” 。只要控制逻辑从比较器的输出接收到“ 1”,上述两个步骤中提到的操作将继续。

-

当$ V_ {i} $小于或等于$ V_ {a} $时,比较器的输出为‘0’ 。因此,控制逻辑从比较器的输出接收到“ 0”。然后,控制逻辑禁用时钟信号发生器,以使其不向计数器发送任何时钟脉冲。

-

此时,计数器的输出将显示为数字输出。它几乎等于相应的外部模拟输入值$ V_ {i} $。

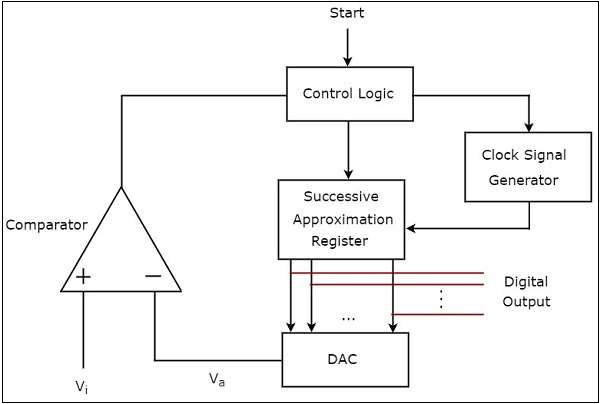

逐次逼近型ADC

逐次逼近型ADC通过内部使用逐次逼近技术产生数字输出,该数字输出近似等于模拟输入。

下图显示了逐次逼近型ADC的框图

逐次逼近型ADC主要由5个模块组成-时钟信号发生器,逐次逼近寄存器(SAR),DAC,比较器和控制逻辑。

逐次逼近ADC的工作如下-

-

当控制逻辑接收到启动命令信号时,它会复位SAR的所有位并启用时钟信号发生器,以便将时钟脉冲发送到SAR。

-

SAR中存在的二进制(数字)数据将根据比较器的输出针对每个时钟脉冲进行更新。 SAR的输出用作DAC的输入。

-

DAC将接收到的数字输入(即SAR的输出)转换为模拟输出。比较器将该模拟值$ V_ {a} $与外部模拟输入值$ V_ {i} $进行比较。

-

只要$ V_ {i} $大于$ V_ {a} $ ,比较器的输出将为’1’。类似地,当$ V_ {i} $小于或等于$ V_ {a} $时,比较器的输出将为’0’。

-

上述步骤中的操作将继续进行,直到数字输出为有效为止。

当数字输出几乎等于相应的外部模拟输入值$ V_ {i} $时,它将为有效输出。

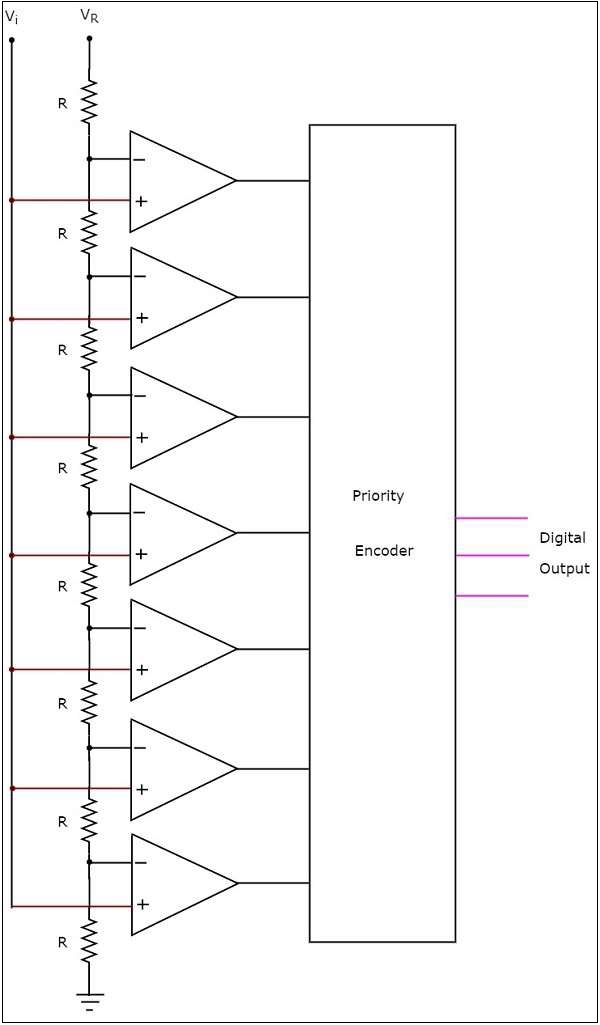

闪存型ADC

闪存型ADC可以立即为相应的模拟输入产生等效的数字输出。因此,闪存型ADC是最快的ADC。

下图显示了3位闪存型ADC的电路图–

3位闪存型ADC由一个分压器网络,7个比较器和一个优先级编码器组成。

3位闪存类型ADC的工作如下。

-

分压器网络包含8个相等的电阻器。在整个网络上相对于地面施加参考电压$ V_ {R} $。每个电阻从底部到顶部相对于地的压降为$ \ frac {V_ {R}} {8} $的整数倍(从1到8)。

-

外部输入电压$ V_ {i} $施加到所有比较器的同相端。从底部到顶部,每个电阻两端相对于地的压降从底部到顶部施加到比较器的反相端子。

-

一次,所有比较器都会将外部输入电压与相应的另一个输入端子上的压降进行比较。这就是说,比较操作由每个比较器并行进行。

-

只要$ V_ {i} $大于相应的另一个输入端子上的压降,比较器的输出将为’1’。类似地,当$ V_ {i} $小于或等于出现在相应的另一个输入端的电压降时,比较器的输出将为’0’。

-

比较器的所有输出均作为优先级编码器的输入连接。该优先级编码器产生一个二进制代码(数字输出),该二进制代码对应于具有“ 1”的高优先级输入。

-

因此,优先级编码器的输出仅是外部模拟输入电压$ V_ {i} $的二进制等效值(数字输出) 。

闪存型ADC用于模拟输入到数字数据的转换速度应非常高的应用中。