先决条件 – 二进制解码器,多路复用器

解码器是一种组合电路,可将二进制信息从![]() 输入行

输入行![]() 独特的输出线。除了输入线,解码器也可能有一个使能输入线。

独特的输出线。除了输入线,解码器也可能有一个使能输入线。

解码器作为解复用器 –

解码器具有使能输入可作为多路分解器的函数。解复用器是一种电路,它接收来自单条线路的信息并将其引导至以下线路之一![]() 可能的输出线。

可能的输出线。

一种![]() 解复用器接收作为输入,

解复用器接收作为输入, ![]() 选择线和一根输入线。这些选择线用于选择一条输出线

选择线和一根输入线。这些选择线用于选择一条输出线![]() 可能的线路。实施一个

可能的线路。实施一个![]() 解复用器,我们使用一个

解复用器,我们使用一个![]() 带启用输入的解码器。这

带启用输入的解码器。这![]() 解复用器的选择线是

解复用器的选择线是![]() 解码器得到的输入线,解复用器的一根输入线是解码器的使能输入。

解码器得到的输入线,解复用器的一根输入线是解码器的使能输入。

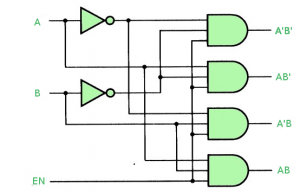

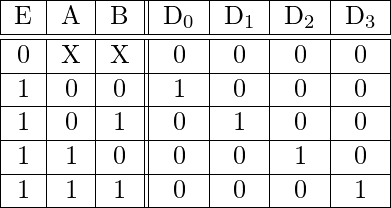

使用具有使能输入的 2:4 解码器制作 1:4 解复用器。设 A、B 为选择线,EN 为解复用器的输入线。

当EN作为数据输入线,A和B作为选择输入时,如下所示的解码器用作2:4解复用器。单个输入变量 E 具有到所有四个输出的路径,但输入信息仅指向输出线之一,如两条选择线 A 和 B 的二进制组合所指定的。 这可以从真值表中验证电路的。

真值表-

使用解码器的组合逻辑实现 –

解码器需要![]() 输入线并有

输入线并有![]() 输出线。这些输出线可以提供

输出线。这些输出线可以提供![]() 最小项

最小项![]() 输入变量。

输入变量。

由于任何布尔函数都可以表示为最小项的总和,因此可以使用可以生成这些最小项以及形成其逻辑和的外部 OR 门的解码器来形成任何布尔函数的电路。

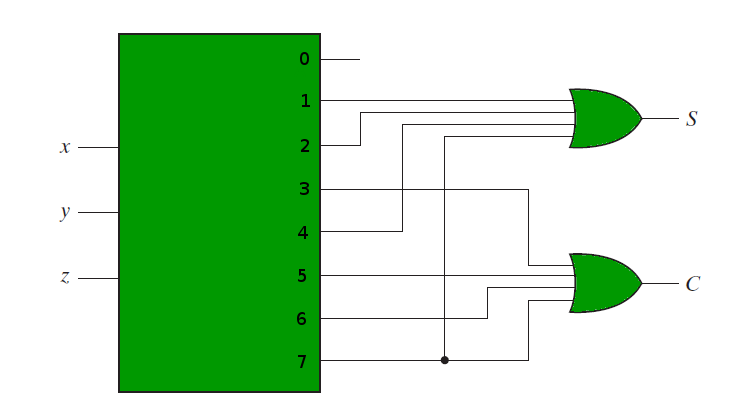

例如,如果我们需要实现全加器的逻辑,我们需要一个 3:8 解码器和或门。全加器的输入、第一位和第二位以及进位位用作解码器的输入。让 x、y 和 z 代表这三位。全加器的 Sum 和 Carry 输出具有以下真值表 –

因此我们有—— ![]()

![]()

以下电路图显示了使用 3:8 解码器和或门实现全加器。

参考-

数字设计,第 5 版,Morris Mano 和 Michael Ciletti