- 组合电路

- 组合电路(1)

- 组合和顺序电路

- 组合和顺序电路

- 组合电路的构建

- 组合电路的构建

- 组合电路的构建(1)

- 组合电路和顺序电路的分类(1)

- 组合电路和顺序电路的分类

- 组合电路和顺序电路的分类(1)

- 组合电路和顺序电路的分类

- 组合电路和顺序电路特性的区别

- 组合电路和顺序电路特性的区别

- 组合电路和顺序电路特性的区别(1)

- 组合电路和顺序电路特性的区别

- 组合电路和顺序电路特性的区别(1)

- 使用解码器的组合电路

- 使用解码器的组合电路

- 使用解码器的组合电路(1)

- 数字算术电路(1)

- 数字算术电路

- 组合电路和时序电路的区别

- 组合电路和时序电路的区别(1)

- 组合电路和时序电路的区别

- 组合电路和时序电路的区别

- 组合电路和时序电路的区别(1)

- 组合电路和时序电路的区别(1)

- VHDL编程组合电路(1)

- VHDL编程组合电路

📅 最后修改于: 2021-01-08 05:46:19 🧑 作者: Mango

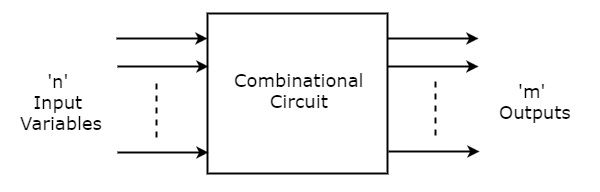

组合电路由逻辑门组成。这些电路以二进制值运行。组合电路的输出取决于当前输入的组合。下图显示了组合电路的框图。

该组合电路具有“ n”个输入变量和“ m”个输出。输入变量的每种组合都会影响输出。

组合电路的设计程序

-

从给定的规格中找到所需数量的输入变量和输出。

-

制定真相表。如果有“ n”个输入变量,那么将有2n种可能的组合。对于每种输入组合,找到输出值。

-

查找每个输出的布尔表达式。如有必要,简化这些表达式。

-

使用逻辑门实现与每个输出对应的上述布尔表达式。

代码转换器

我们在名为代码的章节中讨论了各种代码。将一种代码转换为另一种代码的转换器称为代码转换器。这些代码转换器基本上由逻辑门组成。

例

二进制码到格雷码转换器

让我们实现一个转换器,该转换器将4位二进制代码WXYZ转换为其等效的格雷代码ABCD。

下表显示了4位二进制代码到格雷代码转换器的Truth表。

| Binary code WXYZ | WXYZ Gray code ABCD |

|---|---|

| 0000 | 0000 |

| 0001 | 0001 |

| 0010 | 0011 |

| 0011 | 0010 |

| 0100 | 0110 |

| 0101 | 0111 |

| 0110 | 0101 |

| 0111 | 0100 |

| 1000 | 1100 |

| 1001 | 1101 |

| 1010 | 1111 |

| 1011 | 1110 |

| 1100 | 1010 |

| 1101 | 1011 |

| 1110 | 1001 |

| 1111 | 1000 |

从“真值”表中,我们可以为格雷代码的每个输出位编写布尔函数,如下所示。

$$ A = \ sum m \ left(8,9,10,11,12,13,14,15 \ right)$$

$$ B = \ sum m \ left(4,5,6,7,8,9,10,11 \ right)$$

$$ C = \ sum m \ left(2,3,4,5,10,11,12,13 \ right)$$

$$ D = \ sum m \ left(1,2,5,6,9,10,13,14 \ right)$$

让我们使用4个变量K-Map简化上述功能。

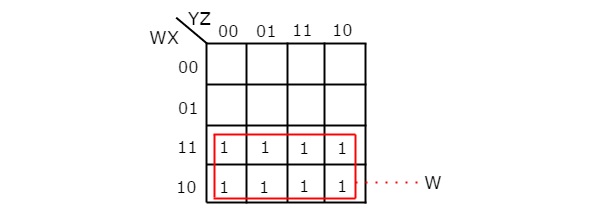

下图显示了用于简化布尔函数A的4个变量K-Map 。

通过将8个相邻的分组,我们得到$ A = W $。

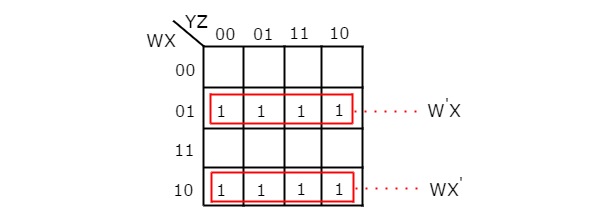

下图显示了用于简化布尔函数B的4个变量K-Map 。

有两组,每组四个相邻。分组后,我们将得到B为

$$ B = {W}’X + W {X}’= W \ oplus X $$

同样,在简化之后,我们将获得以下用于C&D的布尔函数。

$$ C = {X}’Y + X {Y}’= X \ oplus Y $$

$$ D = {Y}’Z + Y {Z}’= Y \ oplus Z $$

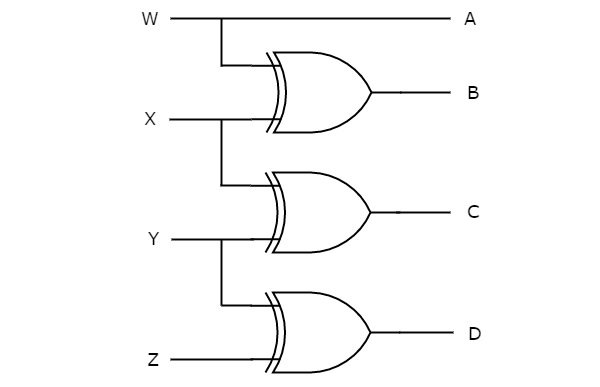

下图显示了4位二进制代码到格雷代码转换器的电路图。

由于输出仅取决于当前输入,因此该4位二进制码到格雷码转换器是组合电路。同样,您可以实现其他代码转换器。

奇偶校验位发生器

根据要生成的奇偶校验位的类型,有两种类型的奇偶校验位生成器。偶校验生成器生成偶校验位。类似地,奇校验位产生器产生奇校验位。

偶校验发生器

现在,让我们为3位二进制输入WXY实现一个偶校验生成器。它生成一个偶数奇偶校验位P。如果输入中存在奇数个1,则偶数奇偶校验位P应该为1,以便结果字包含偶数个1。对于其他输入组合,即使是奇偶校验位,P也应为“ 0”。下表显示了偶校验生成器的真值表。

| Binary Input WXY | Even Parity bit P |

|---|---|

| 000 | 0 |

| 001 | 1 |

| 010 | 1 |

| 011 | 0 |

| 100 | 1 |

| 101 | 0 |

| 110 | 0 |

| 111 | 1 |

从上面的真值表中,我们可以将偶校验位的布尔函数写为

$$ P = {W}'{X}’Y + {W}’X {Y}’+ W {X}'{Y}’+ WXY $$

$ \ Rightarrow P = {W}’\ left({X}’Y + X {Y}’\ right)+ W \ left({X}'{Y}’+ XY \ right)$

$ \ Rightarrow P = {W}’\ left(X \ oplus Y \ right)+ W {\ left(X \ oplus Y \ right)}’= W \ oplus X \ oplus Y $

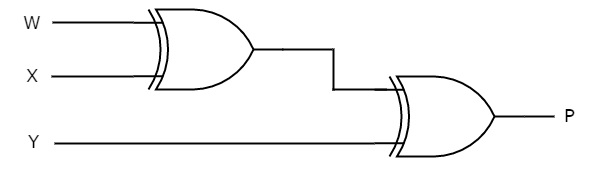

下图显示了偶校验生成器的电路图。

该电路由两个分别具有两个输入的异或门组成。第一异或门具有两个输入W&X,并产生输出W WX。该输出作为第二异或门的一个输入给出。第二个异或门的另一个输入为Y,并产生W⊕X⊕Y的输出。

奇偶校验发生器

如果输入中存在偶数个,则奇校验位P应为1,以使结果字包含奇数个。对于其他输入组合(奇校验位),P应为“ 0”。

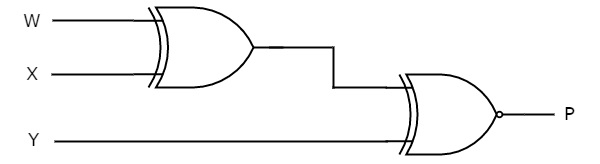

遵循偶数奇偶校验生成器的相同过程来实现奇数奇偶校验生成器。下图显示了奇偶校验发生器的电路图。

上面的电路图由第一级的Ex-OR门和第二级的Ex-NOR门组成。由于奇数奇偶校验与偶数奇偶校验相反,因此我们可以将一个反相器放置在偶数奇偶校验发生器的输出处。在这种情况下,第一和第二级在每个级中都包含一个ExOR门,而第三级则由一个反相器组成。

奇偶校验器

根据必须检查的奇偶校验类型,有两种类型的奇偶校验检查器。偶校验检查器检查传输数据中的错误,该数据包含消息位和偶校验。同样,奇数奇偶校验器检查传输的数据中的错误,该数据包含消息位以及奇数奇偶校验。

偶校验

现在,让我们实现一个偶校验电路。假设一个3位二进制输入WXY与偶数奇偶校验位P一起发送。因此,结果字(数据)包含4位,它将作为偶数奇偶校验器的输入被接收。

它会生成偶数奇偶校验位E。如果接收的数据包含偶数个,则该位将为零。也就是说,接收到的数据没有错误。如果接收到的数据包含奇数个“ 1”,则该偶数奇偶校验位将为“ 1”。就是说,接收到的数据有误。

下表显示了偶校验检查器的“真值”表。

| 4-bit Received Data WXYP | Even Parity Check bit E |

|---|---|

| 0000 | 0 |

| 0001 | 1 |

| 0010 | 1 |

| 0011 | 0 |

| 0100 | 1 |

| 0101 | 0 |

| 0110 | 0 |

| 0111 | 1 |

| 1000 | 1 |

| 1001 | 0 |

| 1010 | 0 |

| 1011 | 1 |

| 1100 | 0 |

| 1101 | 1 |

| 1110 | 1 |

| 1111 | 0 |

从上面的真值表中,我们可以看到,当接收到的数据中存在奇数个奇偶校验位时,其偶数校验位值为“ 1”。这意味着偶校验位的布尔函数是奇函数。异或函数满足此条件。因此,我们可以直接将偶校验位的布尔函数写为

$$ E = W \ oplus X \ oplus Y \ oplus P $$

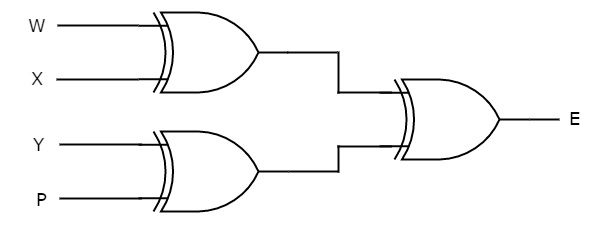

下图显示了偶校验检查器的电路图。

该电路由三个互斥或门组成,每个门有两个输入。一级门产生的输出为$ W \ oplus X $和$ Y \ oplus P $。第二级的异或门产生输出$ W \ oplus X \ oplus Y \ oplus P $

奇偶校验器

假定一个3位二进制输入WXY与奇数奇偶校验位P一起发送。因此,结果字(数据)包含4位,它将作为奇数奇偶校验器的输入被接收。

它生成一个奇数奇偶校验位E。如果接收到的数据包含奇数个“ 1”,则该位将为零。也就是说,接收到的数据没有错误。如果接收到的数据包含偶数个,则此奇数奇偶校验位将为1。就是说,接收到的数据有误。

遵循偶数奇偶校验器的相同过程来实现奇数奇偶校验器。下图显示了奇数奇偶校验器的电路图。

上面的电路图由第一级的Ex-OR门和第二级的Ex-NOR门组成。由于奇数奇偶校验与偶数奇偶校验相反,因此我们可以将一个反相器放置在偶数奇偶校验器的输出处。在这种情况下,第一,第二和第三级包含两个Ex-OR门,一个Ex-OR门和一个反相器。