先决条件 – 组合和顺序电路

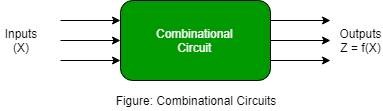

1. 组合电路:

组合电路被定义为不依赖于先前输入来产生任何输出的时间独立电路被称为组合电路。

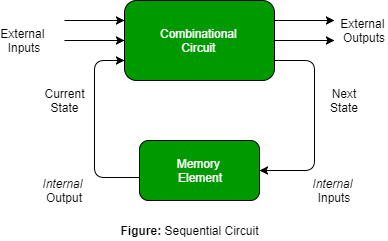

2. 时序电路:

顺序电路是那些依赖于时钟周期并依赖于当前和过去的输入来生成任何输出的电路。

组合电路和时序电路的主要特点如下-

| S.No. | Combinational Circuits | Sequential Circuits | |||

|---|---|---|---|---|---|

| (1) | The output depends only upon the present input and there is no need for feedback for input and output, so memory element is not required. | The output depends upon both present input and present state (previous output), so memory element is required to save the feedback state. | |||

| (2) | It is easier to design, use and handle. | It is not easier to design, use and handle than combinational circuits. | (3) | Clock signals are not required and it is not dependent on time. | Clock signals are required and it is dependent on time and clock so need triggering. |

| (4) | Elementary building blocks are only logic gates. | Elementary building blocks are Flip-Flops. | (5) | These are faster logic circuits. | These circuits are slower than combinational circuits. |