- 数字组合电路

- 数字组合电路(1)

- 组合和顺序电路

- 组合和顺序电路

- 组合电路的构建(1)

- 组合电路的构建

- 组合电路的构建

- 组合电路和顺序电路的分类(1)

- 组合电路和顺序电路的分类

- 组合电路和顺序电路的分类

- 组合电路和顺序电路的分类(1)

- 组合电路和顺序电路特性的区别

- 组合电路和顺序电路特性的区别(1)

- 组合电路和顺序电路特性的区别(1)

- 组合电路和顺序电路特性的区别

- 组合电路和顺序电路特性的区别

- 使用解码器的组合电路

- 使用解码器的组合电路

- 使用解码器的组合电路(1)

- 组合电路和时序电路的区别

- 组合电路和时序电路的区别

- 组合电路和时序电路的区别(1)

- 组合电路和时序电路的区别

- 组合电路和时序电路的区别(1)

- 组合电路和时序电路的区别(1)

- VHDL编程组合电路(1)

- VHDL编程组合电路

- 组合电路|计算机组织和架构教程(1)

- 组合电路|计算机组织和架构教程

📅 最后修改于: 2021-01-12 04:54:57 🧑 作者: Mango

组合电路是一种电路,其中我们组合电路中的不同门,例如编码器,解码器,复用器和解复用器。组合电路的一些特性如下-

-

组合电路在任何时刻的输出仅取决于输入端子上的电平。

-

组合电路不使用任何存储器。输入的先前状态对电路的当前状态没有任何影响。

-

组合电路可以具有n个输入和m个输出。

框图

我们将详细阐述一些重要的组合电路,如下所示。

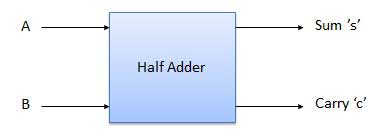

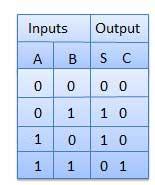

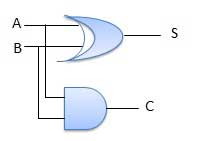

半加法器

半加法器是具有两个输入和两个输出的组合逻辑电路。半加法器电路被设计为将两个单比特二进制数A和B相加。这是两个两个单比特数相加的基本构建块。该电路有两个输出进位和和。

框图

真相表

电路原理图

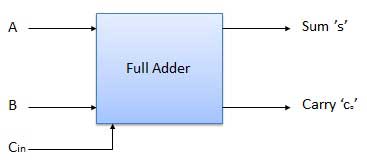

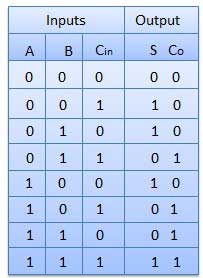

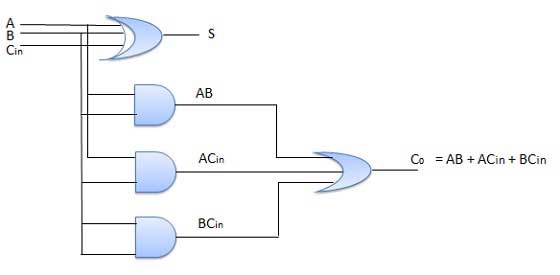

完全加法器

开发全加法器以克服半加法器电路的缺点。它可以将两个一位数字A和B相加,并带有c。全加法器是一个三输入两输出组合电路。

框图

真相表

电路原理图

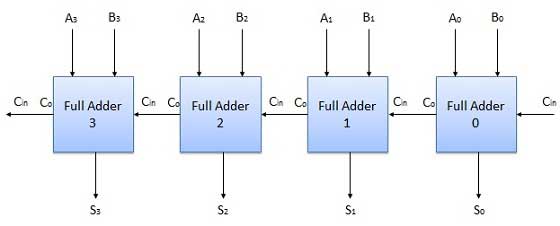

N位并行加法器

Full Adder只能与进位输入相加两个两位数的二进制数。但是在实际中,我们需要添加比仅仅一位长得多的二进制数。要添加两个n位二进制数,我们需要使用n位并行加法器。它级联使用许多完全加法器。前一个完整加法器的进位输出连接到下一个完整加法器的进位输入。

4位并行加法器

在框图中,A 0和B 0代表四个位字A和B的LSB。因此,全加法器-0是最低级。因此,其C in已永久设为0。其余连接与n位并行加法器的连接完全相同,如图2所示。四位并行加法器是非常常见的逻辑电路。

框图

N位并行减法器

减法可以通过将要减去的数字的1或2的补码进行。例如,我们可以通过将B的1或2的补码加到A来执行减法(AB)。这意味着我们可以使用二进制加法器执行二进制减法。

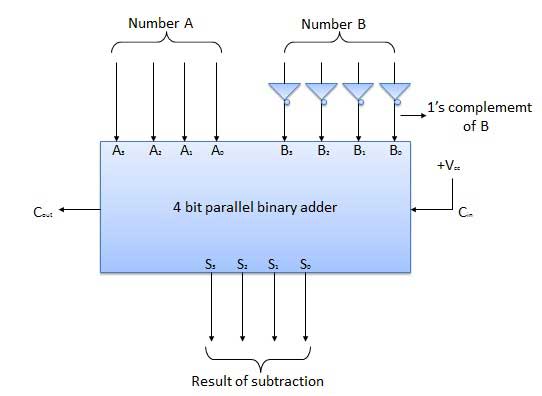

4位并行减法器

要减去的数字(B)首先通过反相器获得其1的补码。然后,4位加法器将A和B的2的补码相加以产生减法。 S 3 S 2 S 1 S 0表示二进制减法(AB)的结果,进位输出C out表示结果的极性。如果A> B,则Cout = 0且二进制形式(AB)的结果,则C out = 1且结果为2的补码形式。

框图

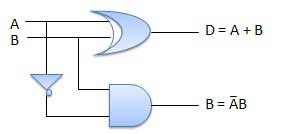

半减法器

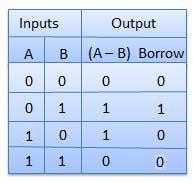

半减法器是具有两个输入和两个输出(差分和借位)的组合电路。它在输入处产生两个二进制位之间的差,并且还产生输出(借位)以指示是否已借入1。在减法(AB)中,A称为Minuend位,B称为Subtrahend位。

真相表

电路原理图

完全减法器

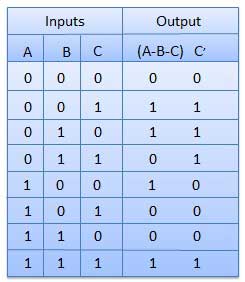

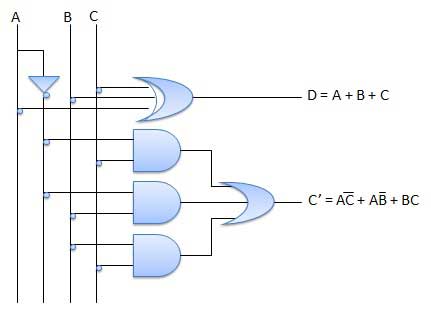

半减法器的缺点被全减法器克服。全减法器是一个组合电路,具有三个输入A,B,C和两个输出D和C’。 A是“被减数”,B是“超额清算”,C是前一阶段产生的“借入”,D是差额输出,C’是借位输出。

真相表

电路原理图

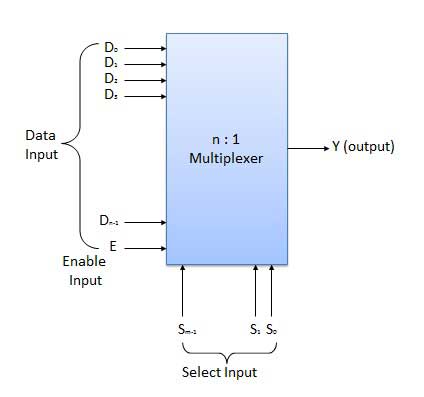

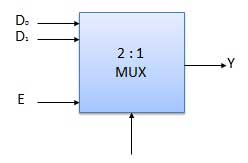

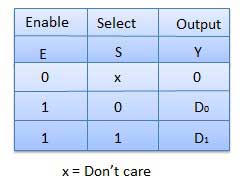

多路复用器

多路复用器是一种特殊类型的组合电路。有n个数据输入,一个输出和m个2m = n的选择输入。它是一个数字电路,它选择n个数据输入之一并将其路由到输出。 n个输入之一的选择由所选输入完成。根据在所选输入上应用的数字代码,从n个数据源中选择一个并将其传输到单个输出Y。E被称为选通或启用输入,对于级联很有用。通常它是一个低电平有效端子,这意味着它将在低电平时执行所需的操作。

框图

多路复用器有多种变化

- 2:1多路复用器

- 4:1多路复用器

- 16:1多路复用器

- 32:1多路复用器

框图

真相表

解复用器

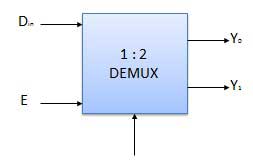

解复用器执行复用器的反向操作,即,它接收一个输入并将其分配到几个输出上。它只有一个输入,n个输出,m个选择输入。一次,选择线仅选择一条输出线,并且输入传输到所选的输出线。解复用器等效于图1所示的单刀多路开关。

解复用器有多种变体。

- 1:2解复用器

- 1:1多路解复用器

- 1:16解复用器

- 1:32解复用器

框图

真相表

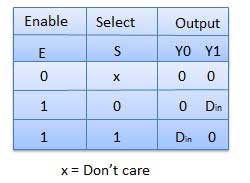

解码器

解码器是组合电路。它具有n个输入,最大m = 2n个输出。解码器与没有任何数据输入的解复用器相同。它执行与编码器完全相反的操作。

框图

以下是解码器的示例。

- 代码转换器

- BCD到七段解码器

- 数码管解码器

- 继电器执行器

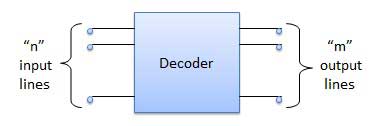

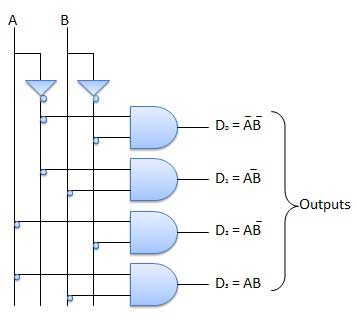

2至4线解码器

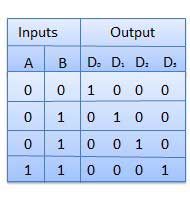

图中显示了2到4行解码器的框图。 A和B是两个输入,其中D到D是四个输出。真值表说明了解码器的操作。它表明,仅对于特定的输入组合,每个输出均为1。

框图

真相表

逻辑电路

编码器

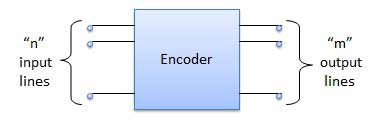

编码器是一种组合电路,旨在执行解码器的逆运算。编码器具有n条输入线和m条输出线。编码器产生对应于数字输入编号的m位二进制代码。编码器接受n个输入数字字并将其转换为m位另一个数字字。

框图

以下是编码器的示例。

- 优先编码器

- 十进制转BCD编码器

- 八进制到二进制编码器

- 十六进制到二进制编码器

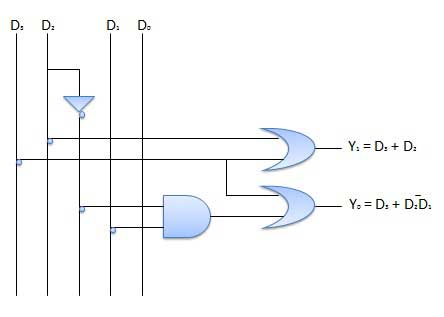

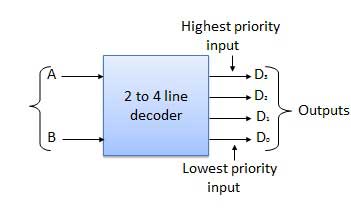

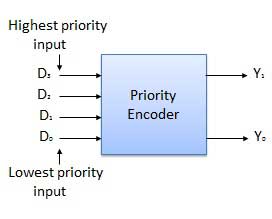

优先编码器

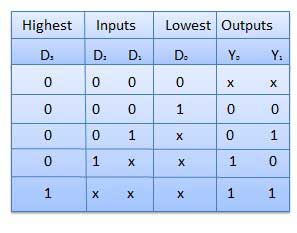

这是一种特殊的编码器。优先考虑输入线。如果两条或多条输入线同时为1,则优先级最高的输入线。有四个输入D 0 ,D 1 ,D 2 ,D 3和两个输出Y 0 ,Y 1 。在四个输入中,D 3具有最高优先级,而D 0具有最低优先级。这意味着,如果D 3 = 1,则Y 1 Y 1 = 11,与其他输入无关。同样,如果D 3 = 0且D 2 = 1,则Y 1 Y 0 = 10,与其他输入无关。

框图

真相表

逻辑电路