阵列乘法器是一种数字组合电路,用于通过使用全加器和半加器阵列将两个二进制数相乘。该数组用于几乎同时添加所涉及的各种乘积项。为了形成各种乘积项,在加法器阵列之前使用了一个与门阵列。

一次检查乘法器的位并形成部分乘积是一种顺序操作,需要一系列加法和移位微操作。两个二进制数的乘法可以通过一次微操作通过组合电路来完成,该电路一次形成所有乘积位。这是一种将两个数字相乘的快速方法,因为所需要的只是信号通过形成乘法阵列的门传播的时间。然而,阵列乘法器需要大量的门,因此直到集成电路的发展才经济。

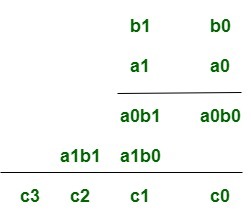

为了用组合电路实现阵列乘法器,考虑两个 2 位数字的乘法,如图所示。被乘数位为 b1 和 b0,乘数位为 a1 和 a0,乘积为

c3c2c1c0

假设 A = a1a0 和 B= b1b0,最终乘积项 P 的各个位可以写成:-

1. P(0)= a0b0

2. P(1)=a1b0 + b1a0

3. P(2) = a1b1 + c1 其中 c1 是在 P(1) 项的加法过程中产生的进位。

4. P(3) = c2 其中 c2 是在 P(2) 项的加法过程中产生的进位。

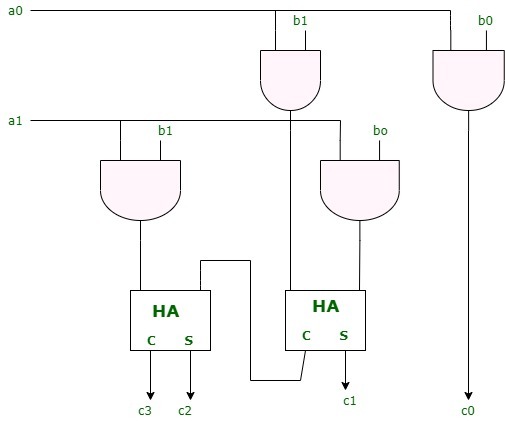

对于上述乘法,需要一个由四个与门组成的阵列来形成各种乘积项,例如 a0b0 等,然后需要一个加法器阵列来计算涉及上述等式中提到的各种乘积项和进位组合的和,以便得到最终的产品位。

- 第一部分积是通过将 a0 乘以 b1、b0 形成的。如果两个位都为 1,则两个位(例如 a0 和 b0)相乘产生 1;否则,它产生 0。这与 AND 操作相同,可以用 AND 门实现。

- 第一部分乘积由两个与门形成。

- 第二个部分乘积由 a1 乘以 b1b0 形成,并向左移动一个位置。

- 以上两个部分乘积加有两个半加器(HA)电路。通常部分乘积中有更多位,因此需要使用全加器来产生总和。

- 请注意,乘积的最低有效位不必通过加法器,因为它是由第一个与门的输出形成的。

可以以类似的方式构造具有更多位的组合电路二进制乘法器。乘法器的一位与被乘数的每一位进行“与”运算,层级与乘法器中的位一样多。每一级与门中的二进制输出与前一级的部分乘积并行相加,形成一个新的部分乘积。最后一层生产产品。对于 j 个乘数位和 k 个被乘数,我们需要j*k 个与门和(j-1) 个k 位加法器来产生j+k 个位的乘积。