数字逻辑中的计数器

根据维基百科,在数字逻辑和计算中,计数器是一种存储(有时显示)特定事件或过程发生次数的设备,通常与时钟信号相关。计数器用于数字电子设备中用于计数目的,它们可以计算电路中发生的特定事件。例如,在 UP 计数器中,计数器会在时钟的每个上升沿增加计数。不仅计数,计数器可以遵循基于我们设计的特定序列,就像任何随机序列 0,1,3,2... 一样。它们也可以在触发器的帮助下设计。

计数器分类

计数器大致分为两类

- 异步计数器

- 同步计数器

1.异步计数器

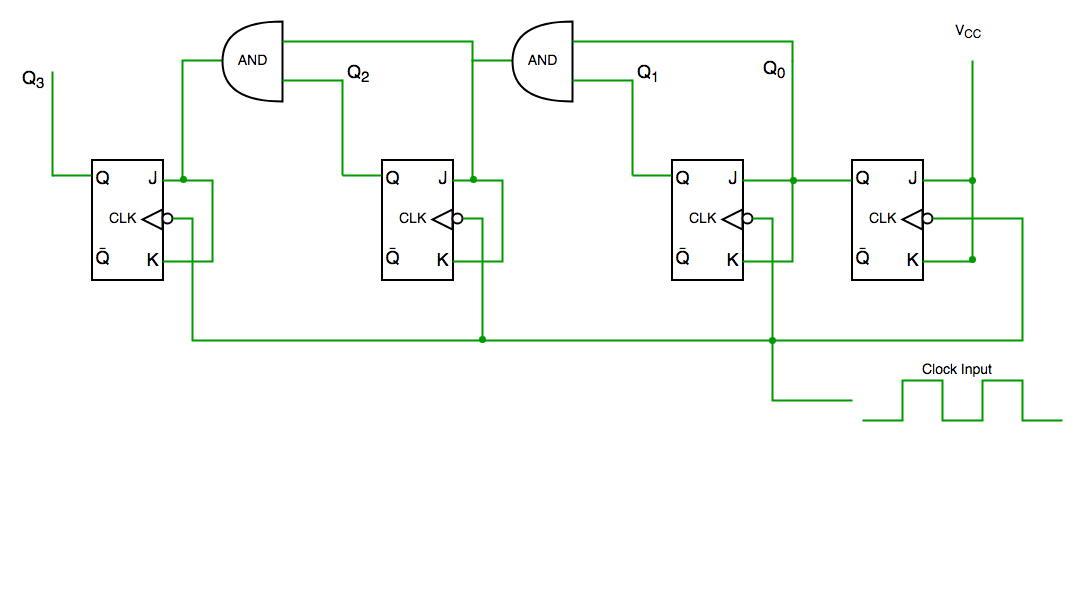

在异步计数器中,我们不使用通用时钟,只有第一个触发器由主时钟驱动,而后一个触发器的时钟输入由前一个触发器的输出驱动。我们可以通过下图来理解——

从时序图中可以明显看出,Q0在遇到时钟脉冲的上升沿时立即变化,Q1在遇到Q0的上升沿时变化(因为Q0就像第二个触发器的时钟脉冲)等等。以这种方式通过 Q0、Q1、Q2、Q3 产生波纹,因此它也被称为波纹计数器。

2.同步计数器

与异步计数器不同,同步计数器有一个驱动每个触发器的全局时钟,因此输出并行变化。同步计数器优于异步计数器的一个优点是,它可以在比异步计数器更高的频率下运行,因为它没有累积延迟,因为每个触发器都有相同的时钟。

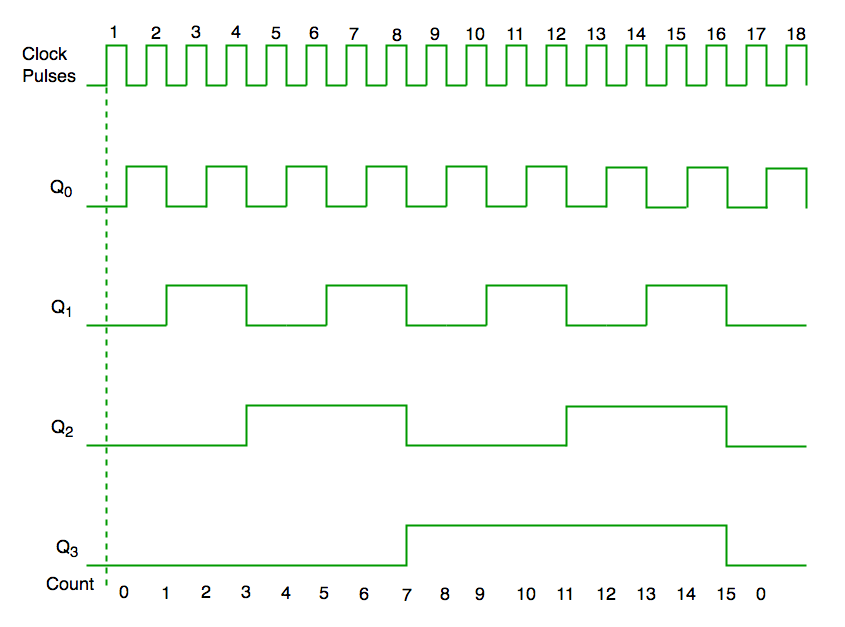

同步计数器电路

时序图同步计数器

从电路图中我们看到,Q0 位响应时钟的每个下降沿,而 Q1 取决于 Q0,Q2 取决于 Q1 和 Q0,Q3 取决于 Q2、Q1 和 Q0。

十年计数器

十年计数器计数十个不同的状态,然后重置为其初始状态。一个简单的十进制计数器将从 0 计数到 9,但我们也可以制作十进制计数器,它可以通过 0 到 15 之间的任何十个状态(对于 4 位计数器)。 Clock pulse Q3 Q2 Q1 Q0 0 0 0 0 0 1 0 0 0 1 2 0 0 1 0 3 0 0 1 1 4 0 1 0 0 5 0 1 0 1 6 0 1 1 0 7 0 1 1 1 8 1 0 0 0 9 1 0 0 1 10 0 0 0 0

简单十年计数器的真值表

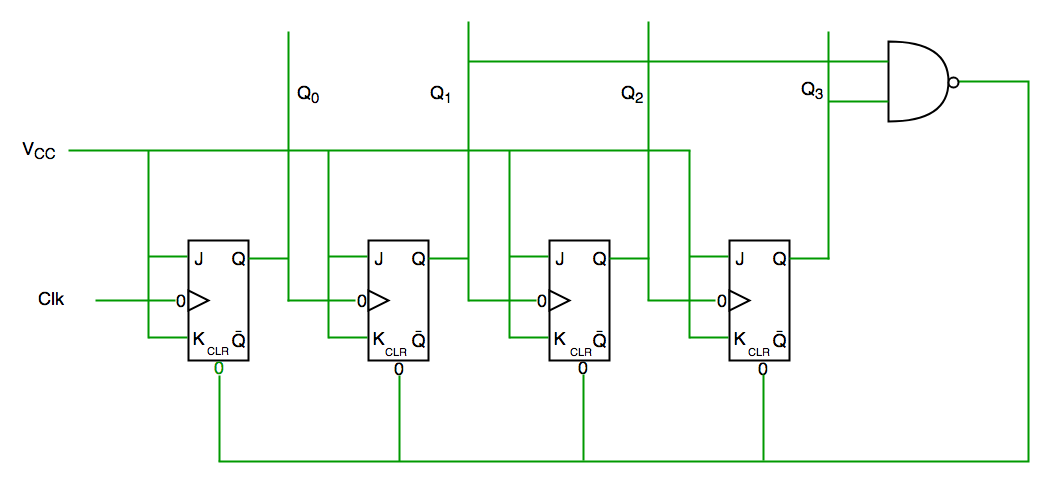

十进制计数器电路图

我们从电路图中看到,我们对 Q3 和 Q1 使用了与非门,并将其馈入以清除输入线,因为 10 的二进制表示是——

1010

我们看到 Q3 和 Q1 在这里是 1,如果我们给这两个位的 NAND 来清除输入,那么计数器将在 10 处被清除并再次从头开始。

要点:计数器中使用的触发器数量始终大于等于 ( log 2 n ),其中 n=计数器中的状态数。

前几年关于柜台的一些门问题

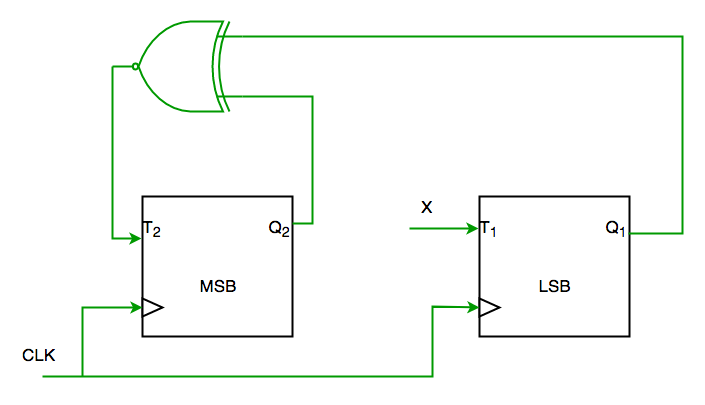

Q1。考虑使用遵循序列 0-2-3-1-0 的 T 触发器的 2 位计数器的部分实现,如下所示

为了完成电路,输入 X 应该是

(一)Q2?

(B) Q2 + Q1

(C) (Q1 - Q2)'

(D) Q1 ?第二季度(GATE-CS-2004)

解决方案:

从电路我们看到

T1=XQ1'+X'Q1——(1)

和

T2=(Q2 ? Q1)'—-(2)

并且期望的输出是 00->10->11->01->00

SO X 应该是Q1Q2'+Q1'Q2满足 1 和 2。

SO ANS 是 (D) 部分。

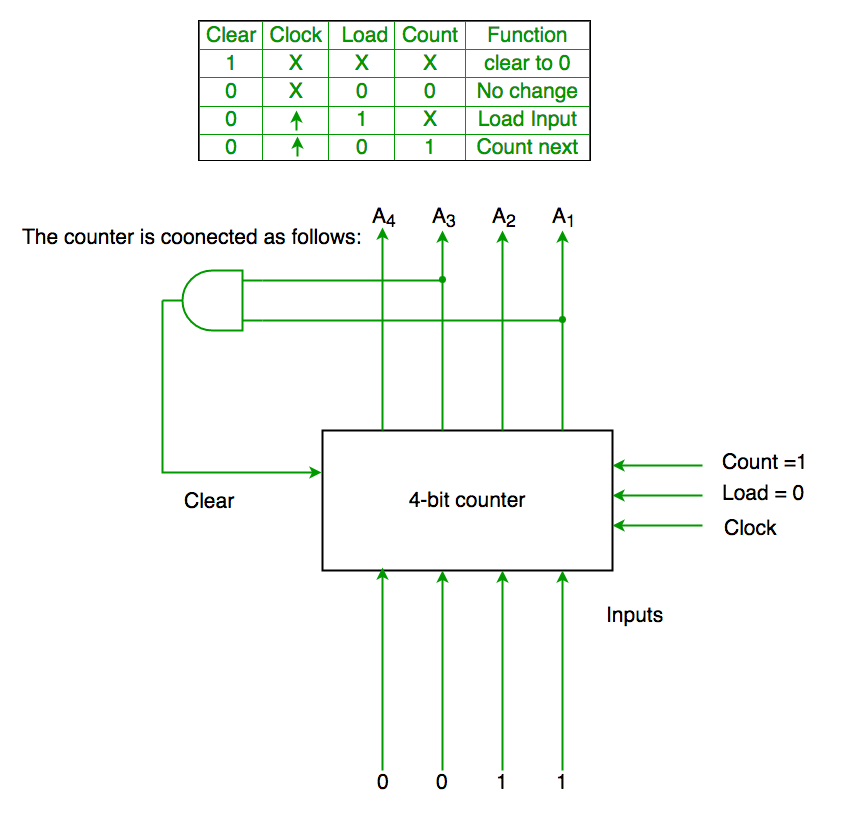

Q2。下面给出了 4 位二进制计数器的控制信号功能(其中 X 表示“无关”)

计数器连接如下:

假设计数器和门延迟可以忽略不计。如果计数器从 0 开始,则它会按以下顺序循环:

(一) 0,3,4

(B) 0,3,4,5

(C) 0,1,2,3,4

(D) 0,1,2,3,4,5 (GATE-CS-2007)

解决方案:

最初 A1 A2 A3 A4 =0000

Clr=A1 和 A3

因此,当 A1 和 A3 都为 1 时,它再次变为 0000

因此 0000(init.) -> 0001(A1 and A3=0)->0010 (A1 and A3=0) -> 0011(A1 and A3=0) -> 0100 ( A1 and A3=1 )[清除条件满足] ->0000(init.) 所以它经过 0->1->2->3->4

Ans 是 (C) 部分。

数字逻辑测验