介绍 :

N 的值可以不同于 2 的幂。此外,计数序列可以是随机的,例如某些循环码(8421、2423 等)。下面的方法用于设计 mod N 和任何计数序列。

Mod-N计数器的设计:

设计步骤是——

第 1 步:决定触发器的数量 –

示例:如果我们正在设计 mod N 计数器并且需要 n 个触发器,那么可以通过此等式找到 n。

N <= 2n这里我们正在设计 Mod-10 计数器 因此,N= 10 并且所需的触发器数量(n)为

对于 n = 3,10<=8,这是错误的。

对于 n= 4,10<=16,这是真的。

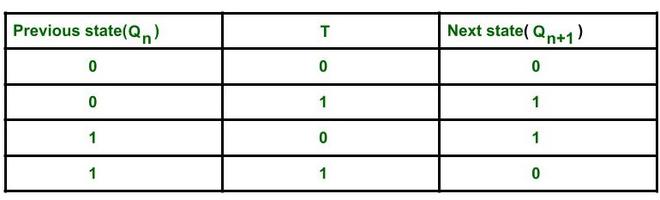

Therefore number of FF required is 4 for Mod-10 counter.第二步:写触发器的激励表——

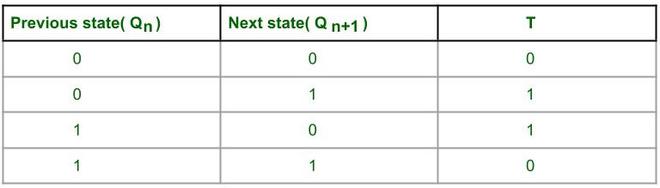

这里使用 T FF

T FF 的励磁表。

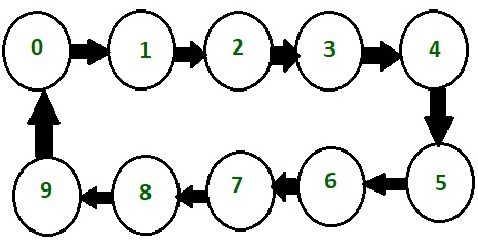

第三步:画出状态图和电路励磁表——

十进制计数器的计数顺序

十进制计数器称为 mod -10 或除以 10 计数器。它从 0 到 9 计数,然后再次重置为 0。它以自然二进制序列计数。这里使用了 4 个 T 触发器。它在 Q 3 Q 2 Q 1 Q 0 = 1001 后复位。

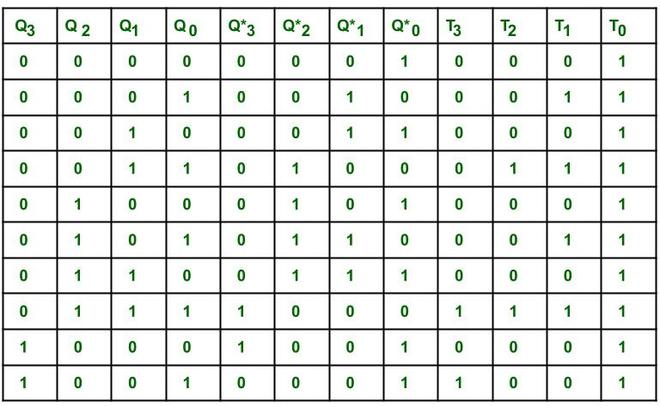

电路励磁表——

这里Q 3 Q 2 Q 1 Q 0是四个触发器的当前状态,Q* 3 Q* 2 Q* 1 Q* 0是4个触发器的下一个计数状态。如果当前状态发生转换,即如果 Q3 值从 0 变为 1 或从 1 变为 0,则相应的 T(toggle) 位写入为 1,否则为 0。

电路励磁表。

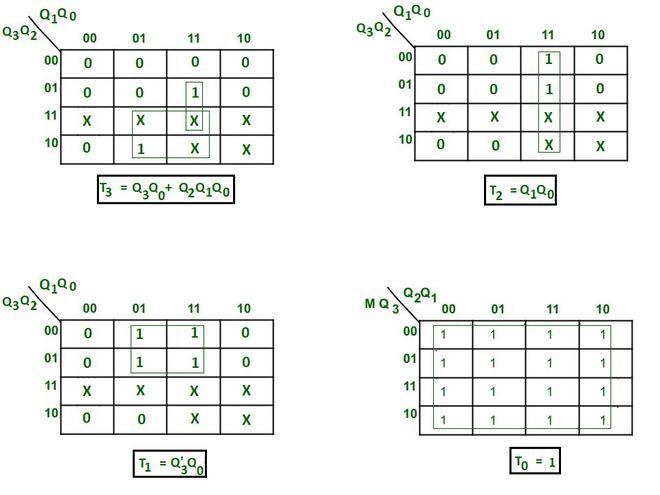

第 4 步:根据触发器输出为每个 FF 输入创建卡诺图作为输入变量 –

简化K图——

用于查找最小表达式的 K 映射。

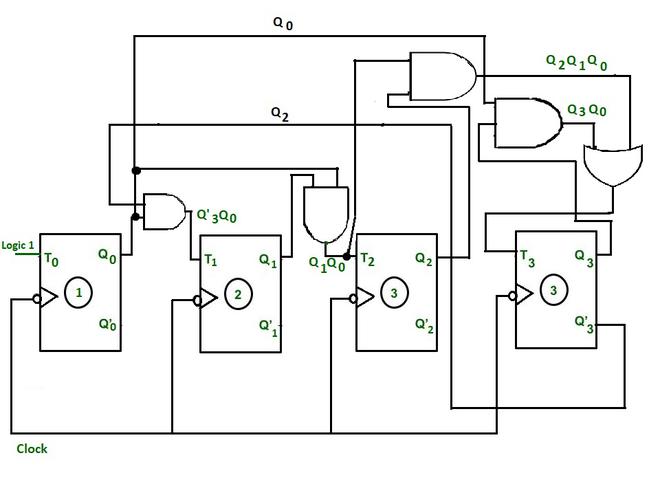

第 5 步:创建电路图 –

这里下降沿触发时钟用于切换目的。

- 时钟在同一时刻提供给每个触发器。

- 根据 K 映射的简化方程,向每个触发器提供切换 (T) 输入。

电路原理图

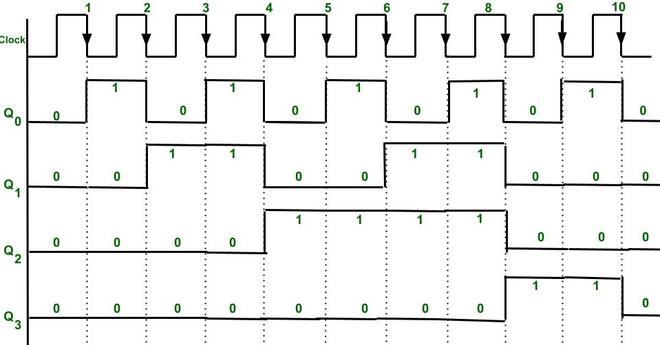

时序图:这里使用切换。

T FF 的特性表。

只有当 FF 的切换输入 (T) 为 1 时,FF 的状态才会改变。

同步Decade计数器时序图

解释 :

- 最初 Q3 Q2 Q1 Q0 是 0 0 0 0 。

- 可以从时序图验证计数器的顺序。在时钟输出的每个下降沿,Q 0 都会翻转,因为 T 0连接到逻辑 1 。

- 仅当表达式 T1 = Q’ 3 Q 0变为 1 时,T 1才变为 1,如果时钟下降沿发生(因为有负沿触发),则 T 1的输出状态即 Q 1将改变。

- 仅当表达式 T2 = Q 1 Q 0变为 1 时,T 2才变为 1,如果出现时钟下降沿,则输出状态 Q2 将改变。

- 仅当表达式 T1 = Q 3 Q 0 + Q 2 Q 1 Q 0 的结果变为 1 时,T 3才变为 1,如果出现时钟下降沿(因为有下降沿触发),则 Q3 的状态将发生变化。

- 我们得到输出为 Q 3 (MSB) Q 2 Q 1 Q 0 (LSB)。

- 在第 10 个下降沿之后,所有 FF 的输出状态再次变为 0 0 0 0。