同步串行进位计数器是这样一种同步计数器,其中触发器的输入以这样的方式连接,只有那些在给定时钟上触发的触发器才会将输入值设为逻辑 1。这个计数器的优点是它减少了解码错误。

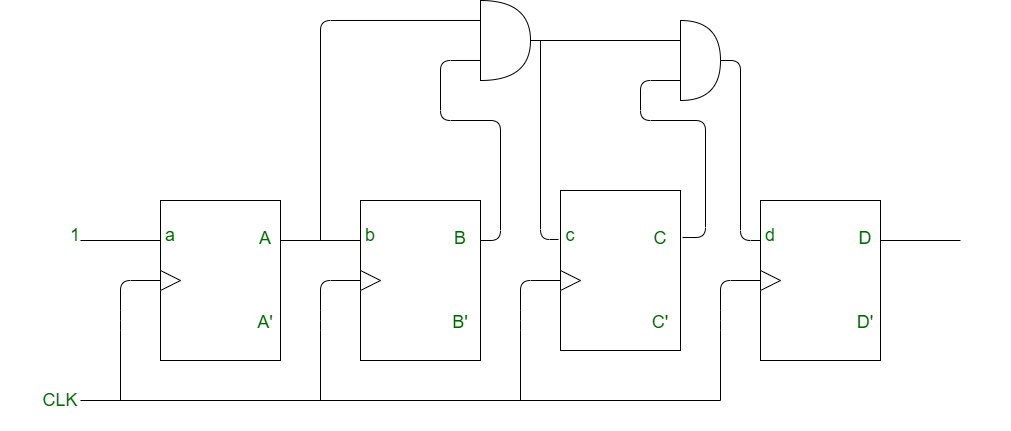

同步串行进位计数器框图:

这是 4 位 (MOD-16) 系列进位计数器的框图。

在上面的柜台:

- 应用每个 CLK 脉冲的切换。

- 当 A = 1 且施加 CLK 脉冲时,B 切换。

- 当 B = 1 且 A = 1 且施加 CLK 脉冲时,C 切换。

- 当 C = B = A = 1 且施加 CLK 脉冲时,D 切换。

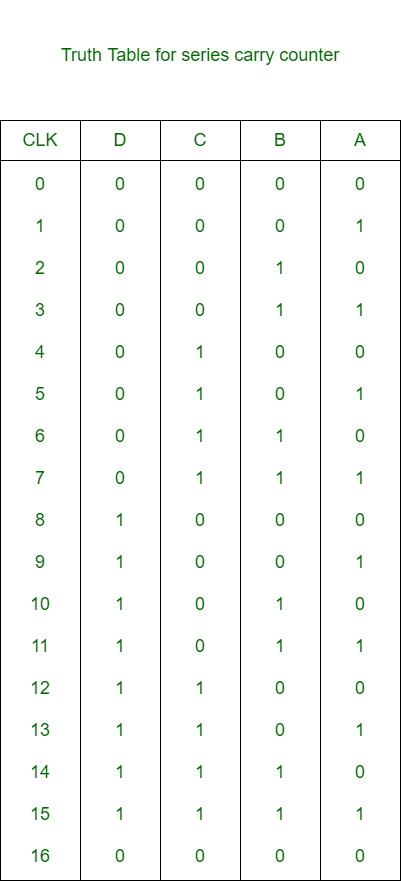

系列进位计数器真值表:

笔记:

为了得到同步递减计数器,每一级的互补输出(A’、B’等)连接到下一级的输入。

总时延:

同步串联进位计数器的总延迟为:

T >= t(pd) + (n-2) x t(pd of AND gate) 随着位数的增加,触发器的传播延迟和与门的传播延迟也增加,这将增加电路的总延迟。

串联进位计数器的优点:

串联进位计数器最重要的优点是它减少了解码错误。