先决条件:计数器,同步计数器。

3 位同步递减计数器:

- 同步计数器时钟同时提供给所有触发器。

- 随着状态数量的增加,电路变得复杂。

- 速度很高。

设计:设计涉及的步骤是

1. 决定人字拖的数量——

N number of Flip flop(FF) required for N bit counter.- 对于 3 位计数器,我们需要 3 FF。

- 最大计数= 2 n -1,其中 n 是位数。

- 对于 n = 3,最大计数 = 7。

- 这里使用了 T FF。

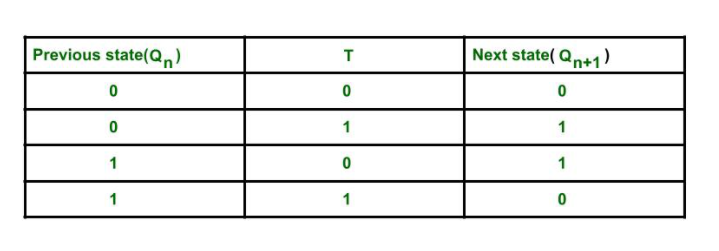

2.写FF的励磁表——

3. 画出状态图和电路励磁表——

状态数 = 2 n,其中 n 是位数。

这里 T = 1,然后有输出状态(下一个状态从前一个状态变化)变化,即 Q 从 0 变为 1 或 1 变为 0

T= 0 那么,没有状态输出状态变化,即 Q 保持不变

4. 使用 k 映射找到简化方程 –

3位同步递减计数器的K图

5. 创建电路图 –

时钟在同一时刻提供给每个触发器。

根据 K 映射的简化方程,向每个触发器提供切换 (T) 输入。

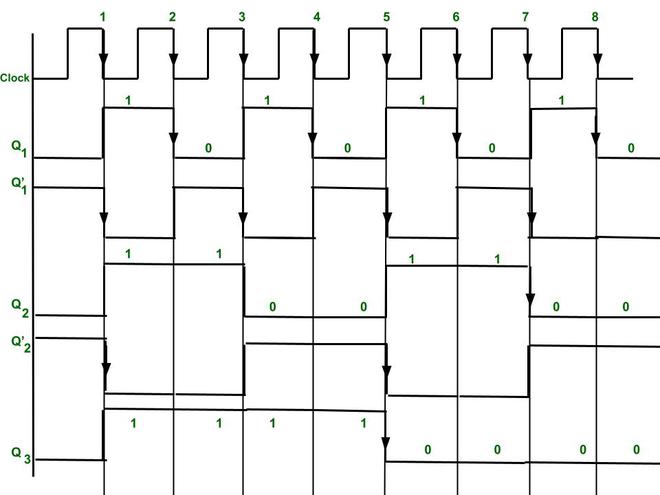

3 位同步减计数器时序图。

说明:

这里 -ve 边沿触发时钟用于切换目的。

正如我们在 T = 1 时的特性表中看到的那样,然后发生切换,T = 0 然后它存储输出状态。

- 最初 Q 3 = 0,Q 2 = 0,Q 1 = 0。

- 在 K 映射的简化方程中,我们得到 T 1 = 1,因此触发器 1 的输出 Q 1在每个下降沿触发(因为时钟是下降沿触发)。触发器(FF) 2 触发输入(T2) 连接到Q’ 1。因此,触发器2 输出状态Q 2仅在时钟下降沿(即-ve 边沿触发)且Q’ 1 =1 时触发.

- 类似地,触发器 3 切换输入 (T) 连接到 Q’2 和 Q’1。因此,当有时钟下降沿且 Q’2=1 和 Q’1 = 1 时,触发器 3 输出是切换的。(从时序图中可以看出)

- 因此,我们得到输出(作为向下计数 Q3(MSB) Q2 Q1(LSB) 在第 8 个边沿触发时钟后三个触发器的输出再次变为 Q3 = 0、Q2 = 0、Q1 =0。

- 我们在每个 -ve 边沿时钟脉冲后得到输出(状态变化)。

- 通过 3 触发器,我们得到的输出为 2 3 -1= 7 比 0。