8051 微控制器中的外部存储器接口

概述 :

对于最小存储器应用,8051 具有内部数据和代码存储器。处于这样的位置。对于某些应用程序,这种内存容量是不够的。要扩展8051单片机的存储空间,必须绑定外部ROM/EPROM和RAM。我们也知道 ROM 用作程序存储器,而 RAM 用作数据存储器。下面我们来看看8051是如何访问这些内存的。

外部程序存储器:

- 当 EA 引脚连接到 Vec 时,程序对地址 0000H 到 OFFFH 的取指被定向到 8051 的内部 ROM,而对地址 1000H 到 FFFFH 的程序取指被定向到外部 ROM/EPROM。当 EA 引脚接地时,程序获取的所有地址(0000H 到 FFFFH)都通向它。

- 设备外部的 ROM/EPROM。如图 1 所示,PSEN 信号用于触发输出 e 外部 ROM/EPROM。

- 端口 0 用作多路复用地址/总线,如图 2 所示。在最初的 T 周期,它提供了一个低位的 8 位地址,后来它被用作数据总线。 8051提供的外部锁存器和ALE信号用于锁存8位地址。

外部程序存储器的时序波形

- Remote ROM/EPROM(Read Only Memory/Electronic Programmable ROM/Electronic Programmable ROM/Electronic Program PSEN 信号用于激活输出 e 外部 ROM/EPROM,如图 1 所示。

- 如图 2 所示,端口 0 用作多路复用地址/总线。它在第一个 T 周期提供低位 8 位地址,然后用作数据总线。 8 位地址使用外部锁存器和 8051 给出的 ALE 信号进行锁存。

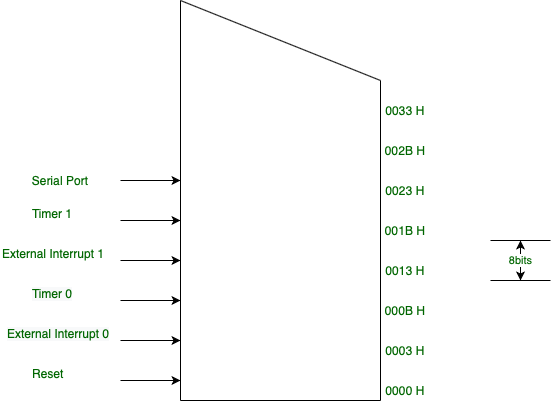

- 1外部中断0为0003H,定时器0为000BH,外部中断1为0013H,定时器1为001BH,以此类推。如果要使用中断,它的操作例程必须与中断在同一位置。如果不使用中断,则服务单元可以用作通用程序存储器。

访问外部 ROM / 程序存储器的说明:

该表解释了访问外部 ROM/程序存储器的指令。Mnemonic Operation MOVC A, @ A+DPTR Copy the contents of the external ROM address formed by adding A and the DPTR, to A MOVC A, @ A + PC This operation will do copy This operation contents of the external ROM address formed by adding A and the PC, to A.

外部存储器接口:

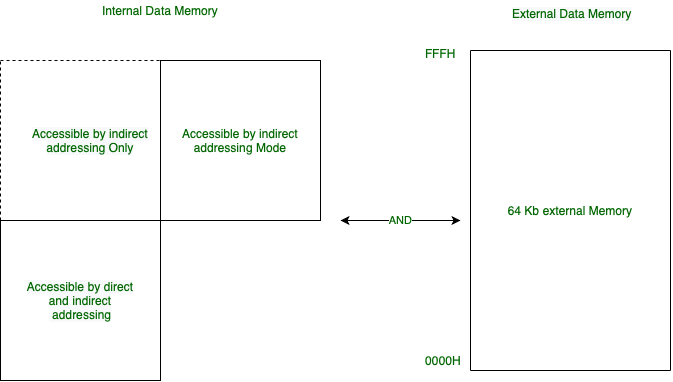

- 8051 最多可以寻址 64 k 字节的附加数据存储器。使用“MOVX”指令访问外部数据存储器。

- 8051 的内部数据存储器分为三个部分:低 128 字节、高 128 字节和 SFR。虽然它们是物理上不同的主体,但高位地址和 SFR 共享同一块地址空间,即 80H x FFH。

- 高地址空间只能通过间接寻址访问,而 SFR 只能通过直接寻址访问,如在高地址空间中所见,另一方面,可以使用直接或间接寻址来访问。

8051 数据存储器的映射 图 5

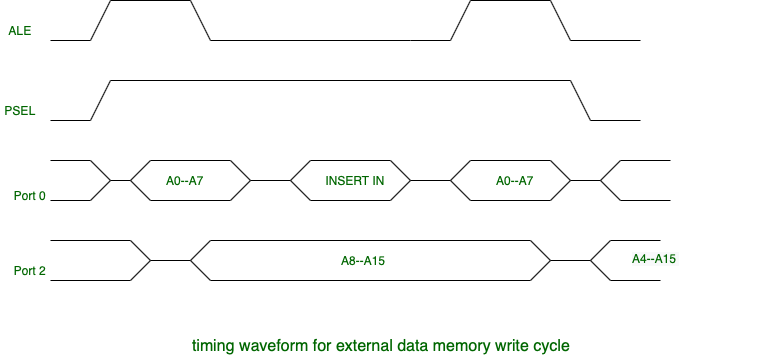

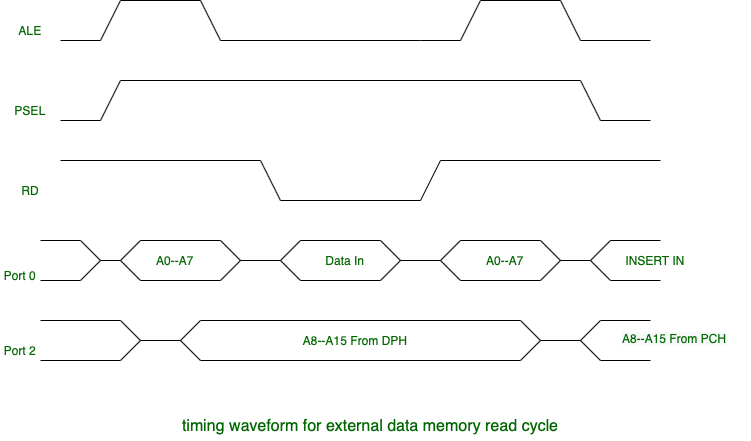

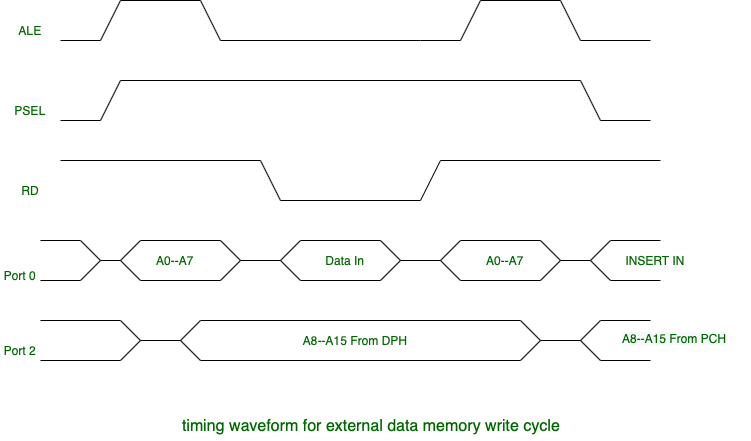

- 图 7 a 和 b 分别显示了外部数据存储器读取和写入周期的时序波形。

7(a)

7(b)

访问外部数据存储器的说明:

下表解释了访问外部数据存储器的指令。Mnemonic Operation MOVX A, @Rp In this operation, it will copy the contents of the external address in Rp to A. MOVX A. @DPTR Copy the contents of the external address in DPTR to A. MOVX @Rp. A Copy data from A to the external address in Rp MOVX DPTR, A Copy data from A to the external address in DPTR.

访问外部存储器时要记住的要点:

- 在访问外部存储器的情况下,所有外部数据通过外部 RAM 或 ROM 移动都涉及 A 寄存器。

- 在访问外部存储器时,R 可以寻址 256 字节,DPTR 可以寻址 64 k 字节

- MOV X 指令用于访问外部 RAM 或 1/O 地址。

笔记 -

必须注意的是,当程序计数器(PC)用于访问外部 ROM 时,它会在加到 A 之前加 1(指向下一条指令)以形成外部 ROM 的物理地址。

内存地址解码:

我们知道读/写存储器由一组寄存器组成,其中每个寄存器都有一个唯一的地址: 存储器的大小是 NX Mas,如图 11.2.1 (a) 所示,其中 N 是寄存器数,M是字长,以位数为单位。

示例 1:

如果内存有 12 条地址线和 8 条数据线,那么寄存器/内存位置的数量 = 2^N= ![]() 字长 = Mbit = 8 位。

字长 = Mbit = 8 位。

示例 2:

- 如果内存有 8192 个内存位置,那么它有:3 个地址线 表 11.2.1 总结了内存接口所需的内存容量和地址线

| Memory Capacity | Address Line Required |

|---|---|

| 1 K = 1024 memory locations | 10 |

| 2 K = 2048 memory locations | 11 |

| 4 K = 4096 memory locations | 12 |

| 8K= 8192 memory locations | 13 |

| 16 K = 16384 memory locations | 14 |

| 32 K = 32768 memory locations | 15 |

| 64 K = 65536 memory locations | 16 |

- 如表所示,内存芯片有 11 条地址线 A10-A0、一个芯片选择 (CS) 和两条控制线。要启用输出缓冲区,请按 RD,要启用输入缓冲区,请按 WR。

- 地址线使用内部解码器进行解码: (b) 显示 4096 (4 K) 寄存器 EPROM(可擦除可编程只读存储器)的逻辑图。

- 它共有 12 个地址块。一个芯片拾取 (CS) 和一个读取控制信号 (A11-A0)。 EPROM 不需要(WR)信号,因为它是只读存储器。

- 内存和 1/0 模块用于微处理器/微控制器框架。由于所有设备共享数据、地址和控制总线,微处理器一次只能与一个设备通信(读/写)。

- 为了与存储器或 I/O 设备连接,必须从微处理器/微控制器中解码地址。解码地址的策略将在下一节中描述。

- 内存接口需要以下组件。

- 选择芯片。

- 识别寄存器。

- 启用适当的缓冲区。

地址解码技术:

- 绝对解码/全解码

- 线性解码/部分解码

技术一:

绝对解码——

- 在这种技术中,所有的高地址线都被解码以选择存储芯片,并且仅针对这些高地址线中定义的逻辑电平选择存储芯片,而没有其他逻辑电平将选择该芯片。

- 完全编码的内存接口如图 11.22 所示。在海量内存结构中,通常使用这种寻址策略。

内存映射 -Memory ICs A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 Address Starting address of EPROM 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0000H End address of EPROM 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1 03FFH Starting address of RAM 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 2000H End address of RAM 0 0 1 0 0 0 1 1 1 1 1 1 1 1 1 1 23FFH

技术2:

线性解码——

- 单独的高阶地址线可用于在紧凑型系统中拾取存储芯片,从而无需用于解码逻辑的硬件。线性解码是这种方法的术语。

- 使用线性编码技术对 RAM 的寻址如图 10 所示。部分解码是该过程的另一个名称。

- 它降低了编码和电路的成本,但它的缺点是需要多个地址(影子地址)。

- 使用线性编码技术对 RAM 的寻址如图 10 所示。反转后,A 是连接到 EPROM 的片选信号,然后连接到 RAM 的片选信号的线。因此,A 线的状态为“空”时选择 EPROM,A15 线的状态为“一”时选择 RAM。由于其他地址线不用于生成芯片拾取信号,因此不考虑它们的状态。

内存映射 -Memory ICs A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 Address Starting address of EPROM 0 x x x x x 0 0 0 0 0 0 0 0 0 0 0000H End address of EPROM 0 x x x x x 1 1 1 1 1 1 1 1 1 1 03FFH Starting address of RAM 1 x x x x x 0 0 0 0 0 0 0 0 0 0 8000H End address of RAM 1 x x x x x 1 1 1 1 1 1 1 1 1 1 83FFH