- 数字电子学中的逻辑门(1)

- 数字电子学中的逻辑门

- 数字电子学中的ASCII代码

- 数字电子学中的ASCII代码(1)

- 数字电子学中的布尔函数

- 数字电子学中的布尔函数(1)

- 数字电子学中的编码器(1)

- 数字电子学中的编码器

- 数字电子学中的布尔代数

- 数字电子学中的2的补语

- 数字电子学中的2的补语(1)

- 数字电子学中的非门(1)

- 数字电子学中的非门

- 数字电子学中的9和10的补语(1)

- 数字电子学中的9和10的补语

- 讨论基础电子学(1)

- 讨论基础电子学

- 数字电子学中的带符号的和无符号的二进制数(1)

- 数字电子学中的带符号的和无符号的二进制数

- SQL |触发器

- 触发器 - SQL (1)

- SQL |触发器(1)

- 基础电子学-有用的资源

- MySQL触发器

- MySQL触发器(1)

- 触发器 - SQL 代码示例

- jquery 触发器 - Javascript (1)

- JK触发器到D触发器的转换

- JK触发器到T触发器的转换

📅 最后修改于: 2020-12-30 06:52:20 🧑 作者: Mango

D触发器

在SR NAND门双稳态电路中,禁止未定义的输入条件SET =“ 0”和RESET =“ 0”。这是SR触发器的缺点。此状态:

- 覆盖反馈锁存动作。

- 强制两个输出均为1。

- 失去输入的控制权,该输入首先变为1,而另一个输入保持为“ 0”,由此可控制锁存器的结果状态。

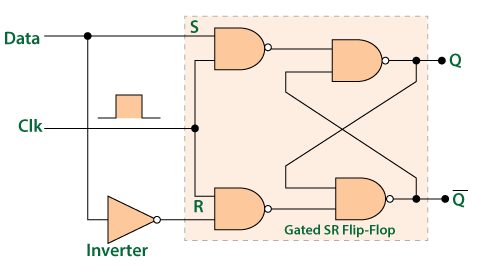

我们需要一个逆变器来防止这种情况的发生。我们将反相器连接到置位和复位输入之间,以产生另一种类型的触发器电路,称为D触发器,延迟触发器,D型双稳态,D型触发器。

D触发器是其他时钟类型中最重要的触发器。它可确保同时两个输入(即S和R)永远不等于1。延迟触发器是使用门控SR触发器设计的,在输入之间连接了一个反相器,从而允许一个输入D(数据)。

单个数据输入(标记为“ D”)代替“设置”输入,对于互补的“复位”输入,则使用逆变器。因此,由电平敏感的SR触发器构成电平敏感的D型或D触发器。

因此,这里S = D和R =〜D(D的补码)

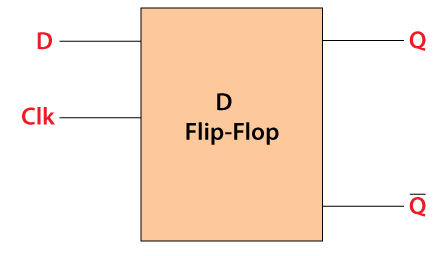

框图

电路原理图

我们知道SR触发器需要两个输入,即一个“设置”输出,另一个“复位”输出。通过使用逆变器,我们可以仅通过一个输入来设置和重置输出,因为现在两个输入信号可以互补。在SR触发器中,当两个输入均为0时,该状态不再可能。 D触发器中的补码消除了这种歧义。

在D型触发器中,单个输入“ D”称为“数据”输入。当数据输入设置为1时,触发器将置位;当数据输入设置为0时,触发器将更改并复位。但是,这将毫无意义,因为触发器的输出将始终在施加到此数据输入的每个脉冲上发生变化。

输入“ CLOCK”或“ ENABLE”可避免这种情况,从而将数据输入与触发器的锁存电路隔离开。当时钟输入设置为true时,D输入条件仅复制到输出Q。这形成了另一个时序器件的基础,称为D Flip Flop 。

当时钟输入设置为1时,触发器的“设置”和“复位”输入都设置为1。因此,在发生时钟转换之前,它不会更改状态并将数据存储在其输出中。简而言之,输出被“锁定”为0或1。

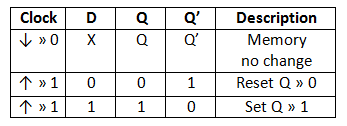

D型触发器的真值表

↓和↑符号表示时钟脉冲的方向。 D型触发器将这些符号假定为边沿触发。