📌 相关文章

- 主从 JK 触发器

- 主从 JK 触发器(1)

- JK触发器(1)

- JK触发器

- JK触发器到D触发器的转换(1)

- JK触发器到T触发器的转换(1)

- JK触发器到D触发器的转换

- JK触发器到T触发器的转换

- JK触发器到T触发器的转换

- JK触发器到D触发器的转换

- JK触发器和SR触发器(1)

- JK触发器和SR触发器

- Verilog | JK触发器

- Verilog | JK触发器(1)

- jk (1)

- 数字电子中的“或”门(1)

- 数字电子中的“或”门

- jk - 任何代码示例

- JK触发器|计算机组织和架构教程

- JK触发器|计算机组织和架构教程(1)

- 电子 (1)

- 循环领域(1)

- 循环领域

- 傀儡主从命令 (1)

- 数字电子教程

- 数字电子教程(1)

- 数字电子中的块编码(1)

- 数字电子中的块编码

- 傀儡主从命令 - 任何代码示例

📜 数字电子领域的主从JK触发器

📅 最后修改于: 2020-12-30 06:54:09 🧑 作者: Mango

主从JK触发器

在“ JK触发器”中,当输入和CLK都长时间设置为1时,则Q输出切换直到CLK为1。因此,将产生不确定或不可靠的输出。此问题在JK触发器中称为“竞赛状态”,可以通过确保仅在很短时间内将CLK设置为1来避免。

说明

主从触发器是通过组合两个触发器的两个输入。 “从”触发器的输出被传递到主触发器的输入。

在“主从触发器”中,除了这两个触发器之外,还使用反相器或“非”门。为了将反相的时钟脉冲传递到“从”触发器,反相器连接到时钟的脉冲。简而言之,当CP对于“ master”设置为false时,CP对于“ slave”设置为true,而当CP对于“ master”设置为true时,CP对于“ slave”设置为false。

加工:

- 当时钟脉冲为真时,从触发器将处于隔离状态,并且系统状态可能受到J和K输入的影响。 “从机”保持隔离状态,直到CP为1。当CP设置为0时,主触发器将信息传递到从触发器以获得输出。

- 由于主触发器是正电平触发,而从触发器是负电平触发,因此主触发器首先要从从响应。

- 当输入J设置为0且K设置为1时,主触发器的输出Q'= 1作为输入K传递到从触发器。时钟迫使从触发器作为复位,然后从触发器进入复位状态。从服务器复制主触发器。

- 当J = 1且K = 0时,输出Q = 1传递到从站的J输入。时钟的负跳变设置从机并复制主机。

- 当输入J和K设置为1时,主触发器在时钟的正跳变上切换。那时,从触发器在时钟的负跳变上切换。

- 当JK触发器的两个输入都设置为0时,该触发器将被禁用,并且Q保持不变。

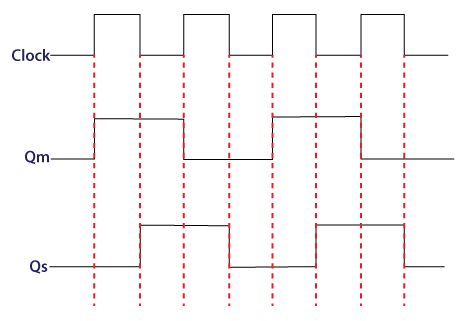

主触发器的时序图:

- 当时钟脉冲设置为1时,主触发器的输出将为1,直到时钟输入保持为0为止。

- 当时钟脉冲再次变为高电平时,主机的输出为0,当时钟再次变为1时,其输出将设置为1。

- 当时钟脉冲为1时,主触发器可工作。从时钟的输出保持为0,直到时钟未设置为0为止,因为从触发器不工作。

- 当时钟脉冲为0时,从触发器可工作。在时钟不再设置为0之前,主触发器的输出保持为1。

- 切换发生在整个过程中,因为输出在循环中更改一次。