- Verilog D闩锁(1)

- C++中的抽象(1)

- C#抽象

- C#抽象(1)

- C++中的抽象

- Verilog数组(1)

- Verilog数组

- Verilog函数(1)

- Verilog函数

- Java中的抽象

- java中的抽象(1)

- Java中的抽象

- Java-抽象

- Java-抽象

- Java中的抽象(1)

- java代码示例中的抽象

- Verilog模块(1)

- Verilog模块

- VLSI设计-Verilog简介

- VLSI设计-Verilog简介(1)

- Verilog参数

- Verilog参数(1)

- Verilog运算符(1)

- Verilog运算符

- Verilog教程

- R 编程中的抽象

- R 编程中的抽象(1)

- Verilog块语句

- Verilog块语句(1)

📅 最后修改于: 2021-01-11 14:34:04 🧑 作者: Mango

设计抽象层

Verilog语言对于理解芯片设计中不同的抽象层至关重要。

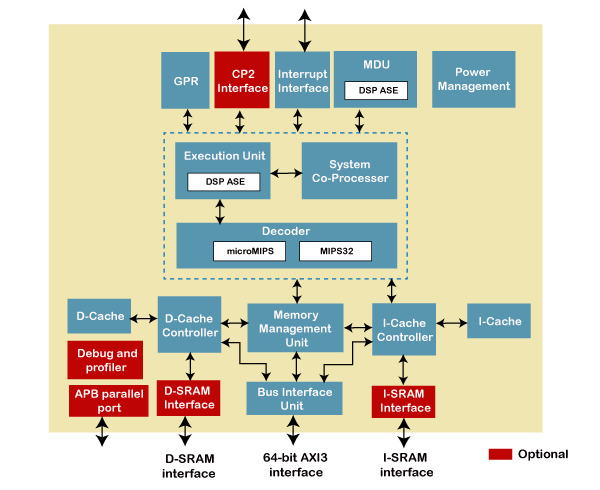

顶层是系统级体系结构,它定义各种子块并根据功能对其进行分组。

例如,处理器群集可以具有多个缓存块,内核和缓存一致性逻辑。所有这些将被表示为具有输入和输出信号的单个块。

在下一个级别,每个子块都用硬件描述语言编写,以准确描述每个块的功能。

在此阶段,将忽略较低级别的实现细节,例如电路原理图,技术库。

例如,一个控制器块将具有多个Verilog文件,每个文件描述一个较小的功能组件。

然后将HDL转换为门级原理图,其中包含技术库,这些技术库可表征触发器等数字元素。

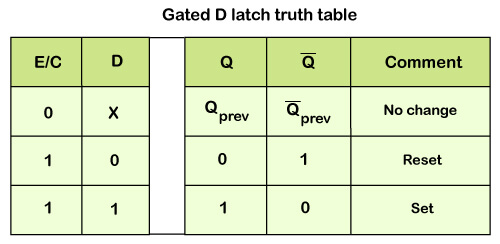

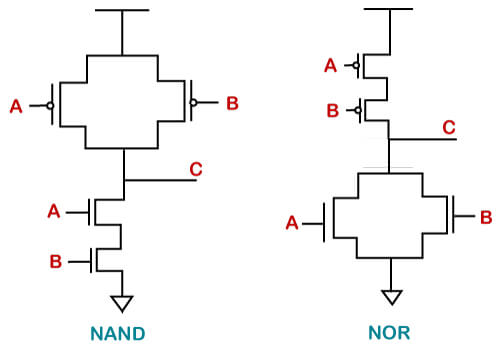

例如,用于D锁存器的数字电路包含以某种方式排列的NAND门,使得D和E输入的所有组合都产生真值表给出的输出Q。

真值表实质上给出了所有输入信号电平和结果输出电平的排列。

硬件原理图也可以使用K-map和布尔逻辑从真值表导出。但是,对于诸如控制器和处理器之类的更复杂的数字块,采用这种方法是没有用的。

NAND门的实现是通过连接特定格式的CMOS晶体管完成的。在此级别上,在设计过程中要考虑晶体管的沟道宽度Vdd和驱动输出电容性负载的能力。

最后一步是使用要制造的EDA工具在硅中布置这些晶体管。在此级别需要一些设备和技术知识,因为不同的布局最终会具有不同的物理特性,例如电阻和电容,以及其他影响。

设计风格

数字模块的设计主要遵循两种样式,一种是自上而下的,另一种是自下而上的方法。

1.自上而下

在这种方法中,首先定义了一个顶级块,并标识了构建该顶级块所需的子模块。

类似地,每个子块被进一步划分为较小的部分,并且该过程一直持续到我们到达叶单元或无法进一步划分的阶段为止。

2.自下而上

第一项任务是确定可用的构建基块。然后将它们放在一起并以某种方式连接以构建更大的单元,并用于将顶层块拼凑在一起。

我们还可以使用两种流程的组合。架构师定义了设计的系统级视图,设计人员实现了每个功能块的逻辑并综合到各个门中。

遵循自上而下的样式,直到这一点。但是,这些门是按照自下而上的流程构建的,从最小的块的物理布局开始,以尽可能最佳的面积,功率和性能。

这些标准单元也具有硬件原理图。并且这些可用于获取各种信息,例如功率的上升和下降,时间和其他延迟。

这些单元可用于综合工具,综合工具会在需要时选择并实例化它们。