- verilog 导入模块 - Python (1)

- Verilog D闩锁

- Verilog D闩锁(1)

- verilog 导入模块 - Python 代码示例

- Verilog数组

- Verilog数组(1)

- Verilog函数

- Verilog函数(1)

- Verilog参数

- Verilog参数(1)

- Verilog运算符(1)

- Verilog运算符

- Verilog教程

- Verilog块语句

- Verilog块语句(1)

- Verilog端口(1)

- Verilog端口

- Verilog分配(1)

- Verilog分配

- Verilog 数据类型

- Verilog数据类型

- Verilog 数据类型(1)

- Verilog数据类型(1)

- Verilog控制块(1)

- Verilog控制块

- Verilog任务(1)

- Verilog任务

- Verilog文件操作(1)

- Verilog文件操作

📅 最后修改于: 2021-01-11 14:37:12 🧑 作者: Mango

Verilog模块

模块是实现某些功能的Verilog代码块。模块可以嵌入其他模块中,并且较高级别的模块可以使用其输入和输出端口与其较低级别的模块进行通信。

句法

模块应包含在module和endmodule关键字内。模块的名称应在module关键字之后给出,也可以声明端口的可选列表。

注意:在端口声明列表中声明的端口不能在模块主体内重新声明。

module ([port_list]);

// Contents of the module

endmodule

// A module can have an empty portlist

module name;

// Contents of the module

endmodule

必须在module和endmodule关键字中定义所有变量声明,函数,任务,数据流语句和下部模块实例。

模块目的

模块代表实现特定行为特征的设计单元,并将在综合过程中转换为数字电路。

可以将输入的任何组合提供给模块,并且它将提供相应的输出。

它允许重用相同的模块,以形成实现更复杂硬件的更重要的模块。

硬件原理图

除了建立较小的模块以形成较大的设计模块外,还可以执行相反的过程。

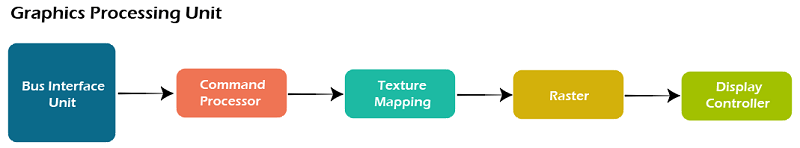

考虑将简单的GPU引擎分解为较小的组件,以便每个组件都可以表示为实现特定功能的模块。

下面的GPU引擎分为五个不同的子块,每个子块执行特定的功能。

总线接口单元将数据从外部输入到设计中,然后由另一个单元处理以提取指令。其他单位沿线处理前一单位提供的数据。

可以将每个子块表示为具有用于与其他模块通信的一组特定的输入和输出信号的模块,并且可以根据需要将每个子块进一步划分为更多子子块。

顶级模块

顶层模块是包含所有其他模块的模块。顶级模块未在任何其他模块中实例化。

例如,设计模块通常在顶级测试平台模块内实例化,以便可以通过提供输入激励来运行仿真。

但是,测试台不会在任何其他模块中实例化,因为它是一个封装了其他所有内容的块。

1.设计顶层

下面显示的设计代码具有一个称为design的顶级模块。它包含完成设计所需的所有其他子模块。

子模块可以具有更多嵌套的子模块,例如mod1内的mod3和mod2内的mod4。

// Design code

module mod3 ( [port_list] );

reg c;

// Design code

endmodule

module mod4 ( [port_list] );

wire a;

// Design code

endmodule

module mod1 ( [port_list] );

wire y;

mod3 mod_inst1 ( );

mod3 mod_inst2 ( );

endmodule

module mod2 ( [port_list] );

mod4 mod_inst1 ( );

mod4 mod_inst2 ( );

endmodule

// Top-level module

module design ( [port_list]);

wire _net;

mod1 mod_inst1 ( );

mod2 mod_inst2 ( );

endmodule

2. Testbench顶层

testbench模块包含一个激励,用于检查设计的功能,并且主要用于通过使用仿真工具进行功能验证。

因此,该设计被实例化并在testbench模块内部称为d0。从模拟器的角度来看,测试平台是顶级模块。

//------------

// Testbench code

// this is the top-level module from simulation perspective

// because 'design' is instantiated within this module

//------------

module testbench;

design d0 ( [port_list_connections] );

//-----------

endmodule

层次名称

当模块可以在内部相互实例化时,便形成了一种层次结构,因此顶层模块称为root 。

由于每个较低的模块都在给定的模块中实例化,该模块应具有不同的标识符名称,因此在访问信号时不会有任何歧义。

层次结构名称由这些标识符的列表构成,这些标识符对于层次结构的每个级别均由点(。)分隔。使用特定信号的分层路径,可以在任何模块内访问任何信号。