- Verilog D闩锁(1)

- Verilog数组(1)

- Verilog数组

- Verilog函数

- Verilog函数(1)

- Verilog模块

- Verilog模块(1)

- Verilog参数(1)

- Verilog参数

- Verilog运算符

- Verilog运算符(1)

- Verilog块语句

- Verilog块语句(1)

- Verilog端口

- Verilog端口(1)

- Verilog分配(1)

- Verilog分配

- Verilog 数据类型(1)

- Verilog 数据类型

- Verilog数据类型(1)

- Verilog数据类型

- Verilog控制块(1)

- Verilog控制块

- Verilog任务

- Verilog任务(1)

- Verilog文件操作

- Verilog文件操作(1)

- Verilog门延迟

- Verilog 4位计数器(1)

📅 最后修改于: 2021-01-11 14:31:15 🧑 作者: Mango

Verilog教程

Verilog是一种硬件描述语言(HDL)。它是用于描述数字系统(例如网络交换机,微处理器,存储器或触发器)的语言。我们可以在任何级别使用HDL来描述任何数字硬件。 HDL中描述的设计与技术无关,非常易于设计和调试,并且通常比示意图更有用,尤其是对于大型电路。

什么是Verilog?

Verilog是一种硬件描述语言(HDL),用于描述数字系统,例如网络交换机或微处理器或触发器的内存。

Verilog的开发旨在简化过程,并使HDL更加强大和灵活。如今,Verilog已成为整个半导体行业使用和实践的最流行的HDL。

HDL的开发旨在通过允许工程师描述所需硬件的功能并使自动化工具将该行为转换为实际的硬件元素(如组合门和顺序逻辑)来增强设计过程。

Verilog类似于任何其他硬件描述语言。它允许设计人员以自下而上或自上而下的方法设计设计。

- 自下而上的设计:电子设计的传统方法是自下而上的。每个设计都是使用标准门在门级别执行的。该设计提供了一种设计新的结构化,分层设计方法的方法。

- 自上而下的设计:它允许早期测试,轻松更改不同的技术以及结构化的系统设计,并提供许多其他好处。

Verilog抽象级别

Verilog支持许多抽象级别的设计,例如:

- 行为水平

- 寄存器转移级别

- 门级

行为水平

行为级别通过并发算法对行为进行描述。每种算法都是顺序的,这意味着它由一组已执行的指令一个接一个地组成。功能,任务和块是主要元素。无需考虑设计的结构实现。

寄存器转移级别

使用寄存器传输级的设计通过操作和寄存器之间的数据传输来指定电路的特性。

RTL代码的现代定义是“任何可合成的代码都称为RTL代码”。

门级

系统的特性由逻辑链接及其在逻辑级别内的时序属性描述。所有信号均为离散信号。它们只能具有确定的逻辑值(“ 0”,“ 1”,“ X”,“ Z”)。

可用的操作是预定义的逻辑原语(基本门)。门级建模可能不是逻辑设计的正确想法。门级代码是使用诸如综合工具之类的工具生成的,其网表用于门级仿真和后端。

Verilog的历史

- Verilog HDL的历史可以追溯到1980年代,当时一家名为Gateway Design Automation的公司开发了逻辑模拟器,Verilog-XL和硬件描述语言。

- Cadence Design Systems在1989年收购了Gateway,并获得了该语言和模拟器的权利。 1990年,Cadence将该语言引入了公共领域,以期成为一种标准的非专有语言。

- Verilog HDL现在由非营利组织Accellera维护,该组织由Open Verilog International(OVI)和VHDL International合并而成。 OVI的任务是通过IEEE标准化程序使用该语言。

- 1995年12月,Verilog HDL成为IEEE标准。 1364年至1995年。一个经过重大修改的版本于2001年发布:IEEE标准。 1364-2001。 2005年进行了进一步的修订,但这仅增加了一些小的更改。

- Accellera还开发了新标准SystemVerilog,该标准扩展了Verilog。

- SystemVerilog在2005年成为IEEE标准(1800-2005)。

Verilog有何用处?

Verilog创建一个抽象级别,以帮助隐藏其实现和技术的细节。

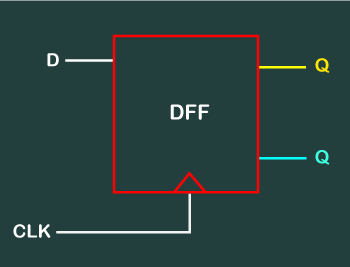

例如,D型触发器设计需要了解如何配置晶体管以实现正沿触发的FF以及将值锁存到触发器所需的上升,下降和CLK-Q时间的知识。其他许多面向技术的细节。

功耗,时序以及驱动网络和其他触发器的能力还需要对晶体管的物理特性有更全面的了解。

Verilog帮助我们专注于行为,其余问题待日后整理。

先决条件

在学习Verilog之前,您应该具有VLSI设计语言的基础知识。

- 您应该知道逻辑图的工作原理,布尔代数,逻辑门,组合和顺序电路,运算符等。

- 您应该了解静态时序分析概念,例如建立时间,保持时间,关键路径,时钟频率限制等。

- ASIC和FPGA基础知识以及综合和仿真概念。

听众

我们的Verilog教程旨在帮助愿意学习如何在Verilog HDL中为数字系统建模以实现自动综合的初学者,设计工程师和验证工程师。在本教程结束时,您将获得Verilog的中级专业知识。

问题

我们向您保证,“ Verilog教程”不会有任何问题。但是,如果有任何错误,请在联系表格中张贴问题。