📌 相关文章

- Verilog块语句

- Verilog块语句(1)

- Verilog D闩锁(1)

- Verilog D闩锁

- Verilog数组(1)

- Verilog数组

- Verilog函数

- Verilog函数(1)

- Object.assign() (1)

- C++ string.Assign()函数(1)

- C++ string.Assign()函数

- Verilog模块

- Verilog模块(1)

- Verilog参数

- Verilog参数(1)

- Lodash _.assign() 方法

- Lodash _.assign() 方法(1)

- JavaScript Object.assign()

- JavaScript 中的 Object.assign()(1)

- JavaScript Object.assign()(1)

- JavaScript 中的 Object.assign()

- Verilog运算符(1)

- Verilog运算符

- Verilog教程

- HTML |位置assign()方法(1)

- HTML |位置assign()方法

- C++中的std :: 字符串:: assign()

- C++中的std :: 字符串:: assign()(1)

- Pandas DataFrame.assign()

📜 Verilog Assign语句

📅 最后修改于: 2021-01-11 14:41:54 🧑 作者: Mango

Verilog分配声明

Assign语句用于驱动网络上的值。它也用于数据流建模。

导线类型或数据类型的信号需要连续分配值。只要将+ 5V电池应用于导线的一端,连接到导线另一端的组件将获得所需的电压。

这个概念是通过assign语句实现的,其中任何电线或其他类似电线(数据类型)都可以用一个值连续驱动。该值可以是常量,也可以是包含一组信号的表达式。

句法

分配语法以关键字assign开头,后跟信号名称,信号名称可以是信号,也可以是不同信号网络的组合。

驱动强度和延迟是可选的,并且大多数用于数据流建模,而不是综合到实际硬件中。

评估右侧的信号并将其分配给左侧的网络或网络表达式。

assign = [drive_strength] [delay]

延迟值对于指定门的延迟很有用,并用于对实际硬件中的时序行为进行建模。该值指示何时应为网络分配评估值。

规则

使用assign语句时需要遵循一些规则:

- LHS应该始终是标量,向量或标量和向量网络的组合,但绝对不能是标量或向量寄存器。

- RHS可以包含标量或向量寄存器以及函数调用。

- 只要RHS上的任何操作数的值发生变化,LHS就会使用新值进行更新。

- Assign语句也称为连续分配。

分配reg变量

我们无法使用assign语句来驱动或分配reg类型变量,因为reg变量能够存储数据并且不会被连续驱动。

Reg信号只能在诸如始终和初始的程序块中驱动。

隐式连续分配

当使用assign语句为给定网络分配一些值时,这称为显式分配

如果声明了要在网上进行的分配,则称为隐式分配。

wire [1:0] a;

assign a = x & y; // Explicit assignment

wire [1:0] a = x & y; // Implicit assignment

组合逻辑设计

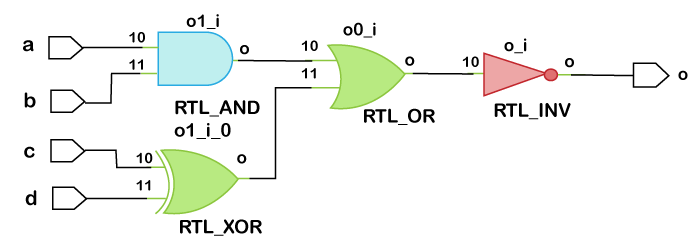

考虑以下由组合门和相应的Verilog代码构成的数字电路。

组合逻辑要求连续驱动输入以维持输出,这与诸如触发器之类的顺序元素不同,在触发器中,值被捕获并存储在时钟的边缘。

分配的语句满足了此目的,因为只要右侧的任何输入发生更改,输出o都会更新。

// This module takes four inputs and performs a Boolean

// operation and assigns output to o.

// logic is realized using assign statement.

module combo (input a, b, c, d, output o);

assign o = ~((a & b) | c ^ d);

endmodule

硬件原理图

完成设计详细说明和综合后,组合电路的行为与assign语句建模的方式相同。

每当RHS上的组合表达式为真时,信号o就变为1。

同样,当RHS为假时,o变为0。输出o是从0ns到10ns的X,因为输入在同一时间是X。