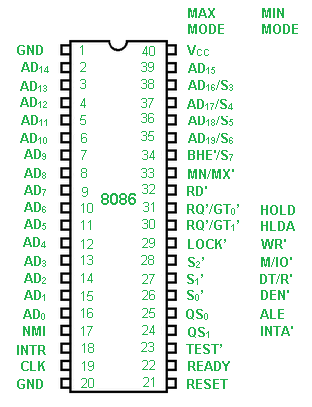

8086微处理器的引脚图如下所示:

英特尔8086是16位HMOS微处理器。它采用40引脚DIP芯片。它使用5V直流电源进行操作。 8086使用20线地址总线。它具有16线数据总线。地址总线的20条线以多路复用模式工作。 16个低位地址总线已与数据复用,而4个高位地址总线已与状态信号复用。

AD0-AD15:地址/数据总线。这些是低阶地址总线。它们与数据复用。当使用AD线传输存储器地址时,将使用符号A代替AD,例如A0-A15。当数据通过AD线传输时,使用符号D代替AD,例如D0-D7,D8-D15或D0-D15。

A16-A19:高阶地址总线。这些与状态信号复用。

S2,S1,S0:状态引脚。这些引脚在T4,T1和T2状态期间处于活动状态,并返回到被动状态(在T3或Tw期间处于1,1,1状态(准备就绪时处于非活动状态)。这些引脚由8288总线控制器用于生成所有内存和I / O操作)访问控制信号。在T4期间S2,S1,S0的任何变化都表示总线周期的开始。

| S2 | S1 | S0 | Characteristics |

|---|---|---|---|

| 0 | 0 | 0 | Interrupt acknowledge |

| 0 | 0 | 1 | Read I/O port |

| 0 | 1 | 0 | Write I/O port |

| 0 | 1 | 1 | Halt |

| 1 | 0 | 0 | Code access |

| 1 | 0 | 1 | Read memory |

| 1 | 1 | 0 | Write memory |

| 1 | 1 | 1 | Passive state |

A16 / S3,A17 / S4,A18 / S5,A19 / S6:指定的地址线与相应的状态信号复用。

| A17/S4 | A16/S3 | Function |

|---|---|---|

| 0 | 0 | Extra segment access |

| 0 | 1 | Stack segment access |

| 1 | 0 | Code segment access |

| 1 | 1 | Data segment access |

BHE’/ S7:总线高电平使能/状态。在T1期间为低电平。它用于使数据进入数据总线最重要的一半D8-D15。连接到数据总线上半部分的8位设备使用BHE(低电平有效)信号。它与状态信号S7多路复用。在T2,T3和T4期间可以使用S7信号。

RD’:用于读取操作。它是一个输出信号。低电平时有效。

就绪:这是从内存或慢速设备确认它们已完成数据传输。设备提供的信号由8284A时钟发生器同步,以为微处理器提供就绪的输入。信号为高电平有效(1)。

INTR:中断请求。这是触发输入。在每个指令的最后一个时钟周期中对它进行采样,以确定请求的可用性。如果发现任何中断请求待处理,则处理器进入中断确认周期。在产生中断使能标志后,可以在内部对其进行屏蔽。该信号为高电平有效(1),并已在内部进行同步。

NMI:不可屏蔽的中断。这是一个边沿触发输入,会导致II型中断。然后,通过位于系统内存中的中断向量查找表来引导子例程。 NMI在内部不可通过软件屏蔽。从低(0)到高(1)的转换会在当前指令的末尾启动中断。此输入已在内部同步。

INTA:中断应答。在每个中断应答周期的T2,T3和Tw期间,它为低电平有效(0)。

MN / MX’:最小/最大。该引脚信号指示处理器将以哪种模式运行。

RQ’/ GT1’,RQ’/ GT0’:请求/授予。这些引脚由本地总线主机使用,用于在微处理器当前总线周期结束时强制微处理器释放本地总线。每个引脚都是双向的。 RQ’/ GT0’比RQ’/ GT1’具有更高的优先级。

LOCK’:其低电平有效引脚。它表示在LOCK’为低电平有效(0)时,不允许其他系统总线主控获得系统总线的控制权。 LOCK信号将一直有效,直到下一条指令完成为止。

TEST(测试):通过“ WAIT”(等待)指令进行检查。如果TEST引脚变为低电平(0),将继续执行,否则处理器将保持空闲状态。在时钟的上升沿,每个时钟周期内,输入都会进行内部同步。

CLK:时钟输入。时钟输入为处理操作和总线控制活动提供了基本时序。它是具有33%占空比的不对称方波。

复位:此引脚要求微处理器立即终止其当前活动。信号必须至少在四个时钟周期内为高电平有效(1)。

Vcc:电源(+ 5V DC)

GND:地线

QS1,QS0:队列状态。这些信号根据下表显示内部8086指令队列的状态

| QS1 | QS0 | Status |

|---|---|---|

| 0 | 0 | No operation |

| 0 | 1 | First byte of op code from queue |

| 1 | 0 | Empty the queue |

| 1 | 1 | Subsequent byte from queue |

DT / R:数据发送/接收。在希望使用8286或8287数据总线收发器的最小系统中,此引脚是必需的。数据流的方向通过收发器控制。

DEN:数据启用。在使用收发器的最小系统中,此引脚用作8286/8287的输出使能。在每个存储器和输入/输出访问期间以及在INTA周期中,DEN为低电平有效(0)。

HOLD / HOLDA: HOLD表示另一个主机正在请求本地总线。这是一个高电平有效(1)。接收到HOLD请求的微处理器将在T4或T1时钟周期的中间发出HLDA(高电平)作为确认。

ALE:地址锁存启用。微处理器提供ALE,以将地址锁存到8282或8283地址锁存器中。在任何总线周期的T1期间,它都是高电平有效(1)脉冲。 ALE信号从不浮动,始终为整数。