ARM 中的流水线

ARM流水线:

- 流水线是RISC(精简指令集计算机)处理器用来执行指令的机制,

- 通过获取指令来加速执行,而其他指令同时被解码和执行。

- 这反过来又允许内存系统和处理器连续工作。

- 每个 ARM 系列的流水线设计都不同。

流水线是一种设计技术或过程,它在提高计算机和微控制器处理器中的数据处理效率方面发挥着重要作用。通过使处理器保持在一个连续的过程中 获取、解码和执行调用(F&E 循环) 。

ARM设备需要流水线,因为 RISC 强调编译器的复杂性。每个阶段相当于1个周期,即n个阶段=n个周期。

管道:

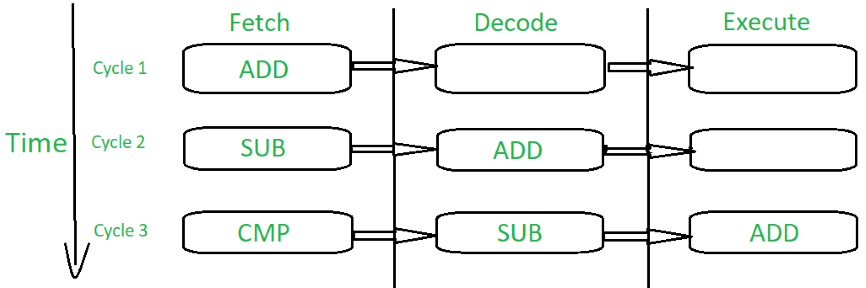

3阶段流水线

- Fetch 从内存中加载一条指令。

- 解码标识要执行的指令。

- Execute 处理指令并将结果写回寄存器。

- 通过重叠执行不同指令的上述阶段,提高了执行速度。

- 流水线允许内核在每个周期执行一条指令,从而提高吞吐量。

ARM流水线特点:

- ARM 流水线不会处理一条指令,直到它完全通过执行阶段。

- 在执行阶段,PC总是指向指令地址+8字节。

- 当处理器处于拇指状态时,PC 总是指向指令地址 + 4 个字节。

- 在执行分支指令或通过直接修改 PC 进行分支时,会导致 ARM 内核刷新其流水线。

- 即使已引发中断,执行阶段的指令也会完成其执行。

手臂 7 –

- 如图所示,它有 3 级流水线。

- 它可以在3个周期内完成它的过程。

- 它具有基本的 F&E 循环,可实现最佳吞吐量。

- 这就是为什么 ARM 7 与其他系列成员相比吞吐量最低的原因。

- 它处理 32 位数据。

手臂 9 –

- ARM 9 中的流水线与 ARM 7 类似,但有 5 个阶段。

- 完成该过程需要5个周期。

5级流水线

- Fetch-它将从内存中获取指令。

- 解码 - 它解码在第一个周期中获取的指令。

- ALU - 它执行在前一阶段已解码的指令。

- LS1(Memory) 加载/存储由加载或存储指令指定的数据。

- LS2(Write) 提取(零或符号)扩展由字节或半字加载指令加载的数据。

- 由于阶段和效率的增加,吞吐量比 ARM 7 高 10%-13%。

- ARM 9 的核心频率略高于 ARM 7 。

手臂 10 –

- 这是一个六级管道。这又需要 6 个周期才能完成该过程。

- 与 ARM 9 相同,但有一个发布阶段,用于检查指令是否准备好在当前阶段解码。

- 它的吞吐量几乎是 ARM 7 的两倍。

- 核心频率高于ARM 9。

6级流水线

流水线的阶段可能会根据每个周期处理的指令集增加或减少(在大多数情况下,阶段倾向于增加以提高效率)。