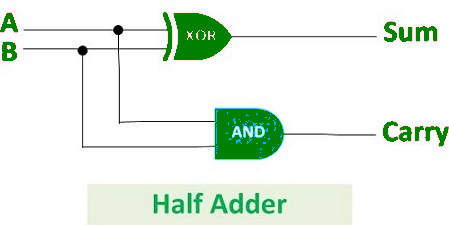

1. 半加法器:

半加器是一种由一个异或门和一个与门相连而设计的组合逻辑电路。半加器电路有两个输入:A 和 B,它们将两个输入数字相加并生成一个进位和一个和。

EX-OR门得到的输出是两个数的和,AND门得到的输出是进位。不会有进位加法的转发,因为没有逻辑门来处理它。因此,这称为半加器电路。

逻辑表达式:

Sum = A XOR B

Carry = A AND B

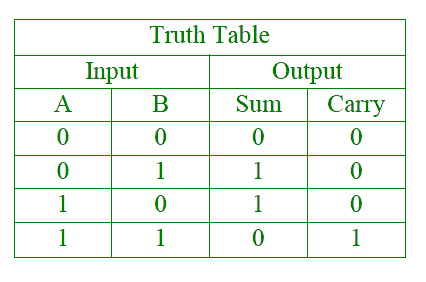

真值表:

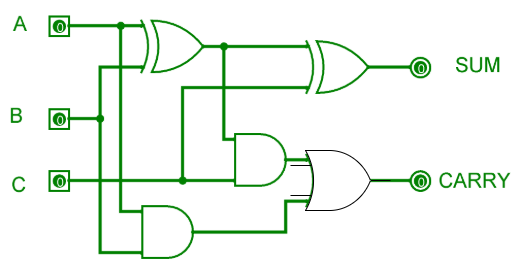

2. 全加器:

全加器是由两个异或门、两个与门和一个或门组成的电路。全加器是将三个输入相加并产生两个输出的加法器,它由两个异或门、两个与门和一个或门组成。前两个输入是 A 和 B,第三个输入是作为 C-IN 的输入进位。输出进位指定为 C-OUT,正常输出指定为 S,即 SUM。

EX-OR门得到的方程是二进制数字之和。而与门得到的输出是加法得到的进位。

真值表:

逻辑表达式:

SUM = (A XOR B) XOR Cin = (A ⊕ B) ⊕ Cin

CARRY-OUT = A AND B OR Cin(A XOR B) = A.B + Cin(A ⊕ B)

半加器和全加器的区别:

| S.No. | Half Adder | Full Adder |

|---|---|---|

| 1 | Half Adder is combinational logic circuit which adds two 1-bit digits. The half adder produces a sum of the two inputs. | Full adder is combinational logical circuit that performs an addition operation on three one-bit binary numbers. The full adder produces a sum of the three inputs and carry value. |

| 2 | Previous carry is not used. | Previous carry is used. |

| 3 | In Half adder there are two input bits ( A, B). | In full adder there are three input bits (A, B, C-in). |

| 4 | Logical Expression for half adder is : S=a⊕b ; C=a*b. |

Logical Expression for Full adder is : S=a⊕b⊕Cin; Cout=(a*b)+(Cin*(a⊕b)). |

| 5 | It consists of one EX-OR gate and one AND gate. | It consists of two EX-OR, two AND gate and one OR gate. |

| 6 | It is used in Calculators, computers, digital measuring devices etc. | It is used in Multiple bit addition, digital processors etc. |