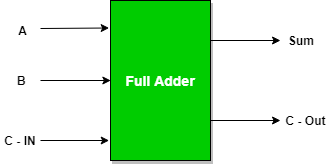

全加器是将三个输入相加并产生两个输出的加法器。前两个输入是 A 和 B,第三个输入是作为 C-IN 的输入进位。输出进位指定为 C-OUT,正常输出指定为 S,即 SUM。

全加器逻辑的设计方式可以将八个输入一起创建一个字节宽的加法器,并将进位位从一个加法器级联到另一个。

全加器真值表:

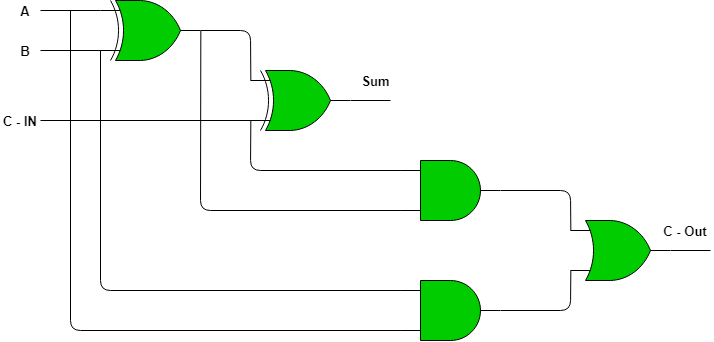

SUM 的逻辑表达式:

= A’ B’ C-IN + A’ B C-IN’ + A B’ C-IN’ + AB C-IN

= C-IN (A’ B’ + AB) + C-IN’ (A’ B + A B’)

= C-IN异或(A XOR B)

= (1,2,4,7)

C-OUT 的逻辑表达式:

= A’ B C-IN + A B’ C-IN + AB C-IN’ + AB C-IN

= AB + B C-IN + A C-IN

= (3,5,6,7)

可以实现 C-OUT 的另一种形式:

= AB + A C-IN + B C-IN (A + A’)

= AB C-IN + AB + A C-IN + A’ B C-IN

= AB (1 +C-IN) + A C-IN + A’ B C-IN

= AB + A C-IN + A’ B C-IN

= AB + A C-IN (B + B’) + A’ B C-IN

= AB C-IN + AB + A B’ C-IN + A’ B C-IN

= AB (C-IN + 1) + A B’ C-IN + A’ B C-IN

= AB + A B’ C-IN + A’ B C-IN

= AB + C-IN (A’ B + A B’)

因此 COUT = AB + C-IN (A EX – OR B)

全加器逻辑电路。

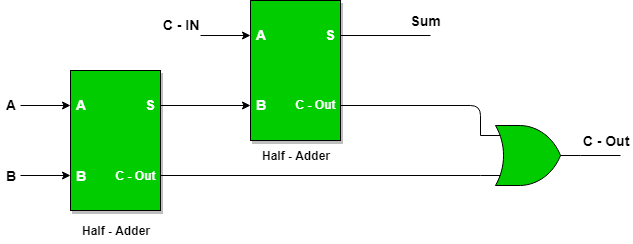

使用半加器实现全加器

实现全加器需要 2 个半加器和一个或门。

使用该逻辑电路,可以将两位相加,从下一个较低的数量级获取进位,并将进位发送到下一个较高的数量级。

使用与非门实现全加器:

使用或非门实现全加器:

实现全加器需要总共 9 个或非门。