在布尔代数中,有三个基本运算, 类似于命题逻辑中的析取、合取和否定。这些操作中的每一个都有相应的逻辑门。除此之外,还有一些其他的逻辑门。

逻辑门——

- AND gate(.) –如果两个输入都是 1,AND 门给出的输出为 1,否则给出 0。

- OR 门(+) –如果两个输入中的任何一个为 1,则 OR 门给出的输出为 1,否则给出 0。

- NOT gate(‘) – NOT 门给出 1 的输出,输入为 0,反之亦然。

- 异或门(

*** QuickLaTeX cannot compile formula: *** Error message: Error: Nothing to show, formula is empty) –如果两个输入不同,则 XOR 门的输出为 1,如果它们相同,则为 0。

如果上述门的输出被否定,则获得三个以上的逻辑门。

- 与非门(

*** QuickLaTeX cannot compile formula: *** Error message: Error: Nothing to show, formula is empty)-与非门(与非门)如果两个输入都是 1,则输出 0,否则输出 1。

- 或非门(

*** QuickLaTeX cannot compile formula: *** Error message: Error: Nothing to show, formula is empty)-如果两个输入都是 0,则 NOR 门(否定的 OR)输出 1,否则输出 0。

- 异或门(

*** QuickLaTeX cannot compile formula: *** Error message: Error: Nothing to show, formula is empty)- XNOR 门(否定 XOR)的输出为 1,两个输入相同,如果两个输入不同,则为 0。

每个逻辑门都有一个与之相关的图形表示或符号。下图显示了与每个逻辑门相关的图形符号和真值表。

通用逻辑门 –

在上面讨论的七个逻辑门中,NAND 和 NOR 也被称为通用门,因为它们可用于实现任何数字电路而无需使用任何其他门。这意味着每个门只能由 NAND 或 NOR 门创建。

使用 NAND 和 NOR 门的三个基本门的实现如下所示 –

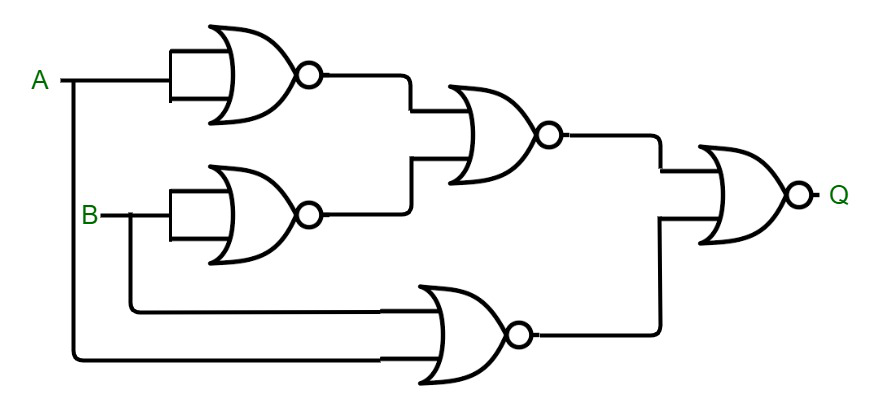

对于异或门,NAND 和 NOR 实现是 –

使用 NAND实现 –

使用 NOR实现 –

注 –为了实现 XNOR 门,可以将单个 NAND 或 NOR 门添加到上述电路中以否定 XOR 门的输出。

GATE CS 角问题:

练习以下问题将帮助您测试您的知识。所有问题都在前几年的 GATE 或 GATE 模拟测试中提出。强烈建议您练习它们。

1. GATE CS 2013,问题 21

2. GATE CS 2012,问题 10

3. GATE CS 2007,问题 33

4. GATE CS 2005,问题 15

参考 –

数字设计,第 5 版,Morris Mano 和 Michael Ciletti