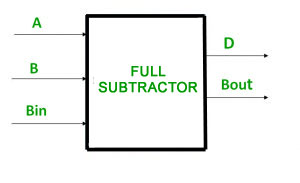

全减法器是一种组合电路,它执行两位减法,一个是被减数,另一个是被减数,同时考虑到前一个相邻的低被减数位的借位。该电路具有三个输入和两个输出。三个输入 A、B 和 Bin 分别表示被减数、减数和前借位。两个输出 D 和 Bout 分别代表差值和输出借位。

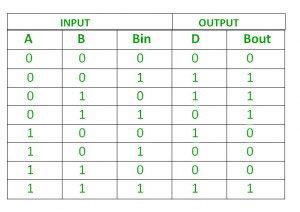

真值表——

从上表中,我们可以绘制 K-Map,如“差异”和“借用”所示。

差异的逻辑表达 –

D = A’B’Bin + A’BBin’ + AB’Bin’ + ABBin

= Bin(A’B’ + AB) + Bin’(AB’ + A’B)

= Bin( A XNOR B) + Bin’(A XOR B)

= Bin (A XOR B)’ + Bin’(A XOR B)

= Bin XOR (A XOR B)

= (A XOR B) XOR Bin

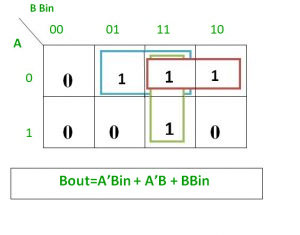

借用的逻辑表达式 –

Bout = A’B’Bin + A’BBin’ + A’BBin + ABBin

= A’B’Bin +A’BBin’ + A’BBin + A’BBin + A’BBin + ABBin

= A’Bin(B + B’) + A’B(Bin + Bin’) + BBin(A + A’)

= A’Bin + A’B + BBin

OR

Bout = A’B’Bin + A’BBin’ + A’BBin + ABBin

= Bin(AB + A’B’) + A’B(Bin + Bin’)

= Bin( A XNOR B) + A’B

= Bin (A XOR B)’ + A’B

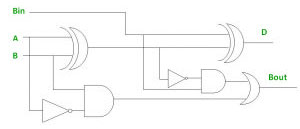

全减法器的逻辑电路 –

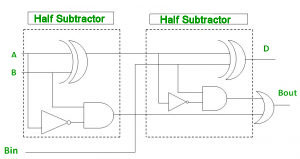

使用半减法器实现全减法器 –

实现全减法器需要 2 个半减法器和一个或门。

参考 –全减法器 – 维基百科