组合逻辑电路框图:

组合逻辑电路注意事项:

- 输出取决于输入的组合。

- 输出只是当前输入的纯函数,即先前状态输入不会对输出产生任何影响。此外,它不使用内存。

- 换句话说,

OUTPUT=f(INPUT) - 输入称为电路的激励,输出称为组合逻辑电路的响应。

组合逻辑电路的分类:

1. 算术:

- 加法器

- 减法器

- 乘数

- 比较器

2. 数据处理:

- 多路复用器

- 解复用器

- 编码器和解码器

3. 代码转换器:

- BCD 到 Excess-3 代码,反之亦然

- BCD 到格雷码,反之亦然

- 七段

半加器和全加器的设计:

- 执行两个单个位相加的组合逻辑电路称为半加器。

- 执行三个单个位相加的组合逻辑电路称为全加器。

1. 半加法器:

- 它是一种算术组合逻辑电路,旨在执行两个单个位的加法。

- 它包含两个输入并产生两个输出。

- 输入称为Augend 和Added bits,输出称为Sum 和Carry。

让我们观察单个位的添加,

0+0=0

0+1=1

1+0=1

1+1=10由于 1+1=10,结果必须是两位输出。所以,上面可以改写为,

0+0=00

0+1=01

1+0=01

1+1=101+1 的结果是 10,其中“1”是进位输出(C out ),“0”是和输出(正常输出)。

半加器真值表:

下一步是绘制逻辑图。要绘制逻辑图,我们需要布尔表达式,可以使用 K-map(卡诺图)获得。由于有两个输出变量’S’和’C’,我们需要为每个输出变量定义K-map。

输出变量 Sum ‘S’ 的 K 映射:

K-map 是乘积形式的总和。得到的方程是

S = AB' + A'B 逻辑上可以写成,

S = A xor B输出变量 Carry ‘C’ 的 K 映射:

从 K-map 得到的方程是,

C = AB使用布尔表达式,我们可以绘制逻辑图如下..

限制:

在半加法器中不能添加进位。

2. 全加器:

- 为了克服半加器面临的上述限制,实现了全加器。

- 它是一个算术组合逻辑电路,执行三个单比特的加法。

- 它包含三个输入(A、B、C in )并产生两个输出(Sum 和 C out )。

- 其中,C in -> Carry In and C out -> Carry Out

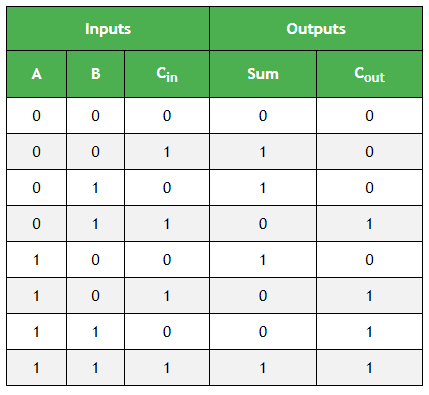

全加器真值表:

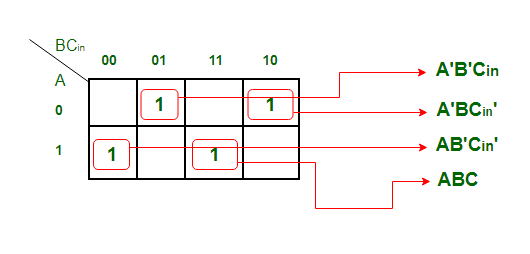

输出变量 Sum ‘S’ 的 K-map 简化:

得到的方程是,

S = A'B'Cin + AB'Cin' + ABC + A'BCin' 方程可以简化为,

S = B'(A'Cin+ACin') + B(AC + A'Cin')

S = B'(A xor Cin) + B (A xor Cin)'

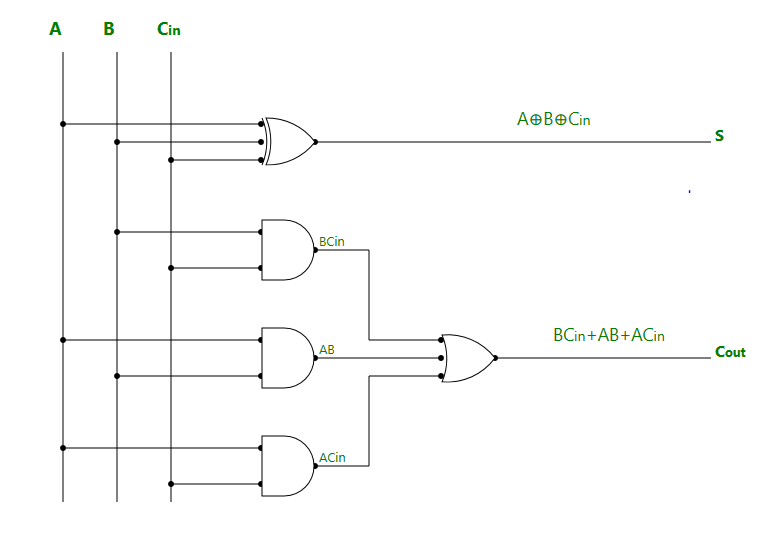

S = A xor B xor Cin 输出变量 ‘C out ‘ 的 K-map 简化

得到的方程是,

Cout = BCin + AB + ACin 全加器逻辑图:

3. 半减法器:

- 它是一种组合逻辑电路,旨在执行两个单个位的减法。

- 它包含两个输入(A 和 B)并产生两个输出(Difference 和 Borrow-output)。

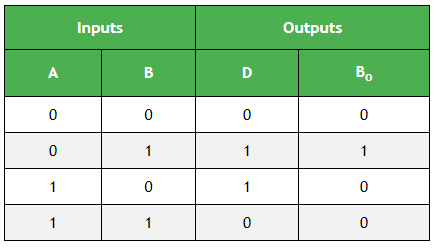

半减法器真值表:

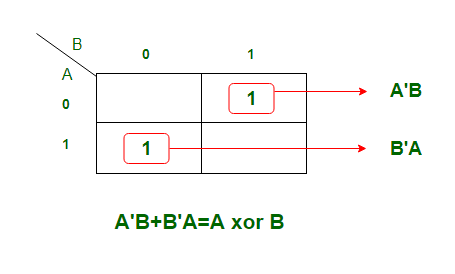

输出变量 ‘D’ 的 K-map 简化:

得到的方程是,

D = A'B + AB'逻辑上可以写成,

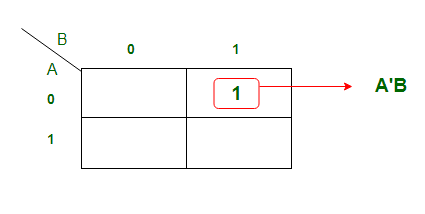

D = A xor B 输出变量 ‘B out ‘ 的 K-map 简化:

从上面的K-map得到的方程是,

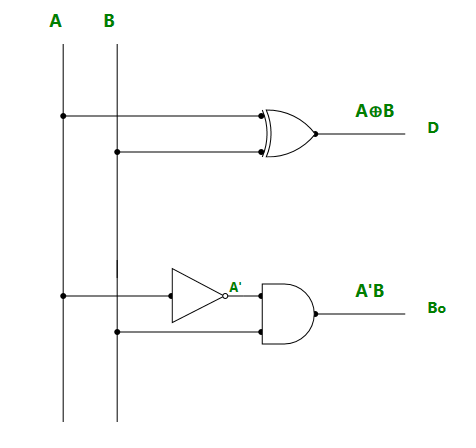

Bout = A'B 半减法器逻辑图:

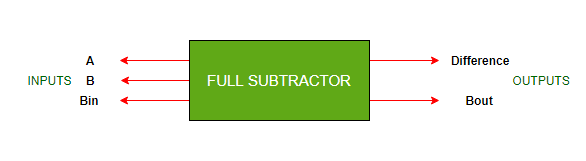

4. 全减法器:

- 它是一种组合逻辑电路,旨在执行三个单个位的减法。

- 它包含三个输入(A、B、B in )并产生两个输出(D、B out )。

- 其中,A 和 B 称为被减数和减数位。

- 并且,B in -> Borrow-In 和 B out -> Borrow-Out

全减法器真值表:

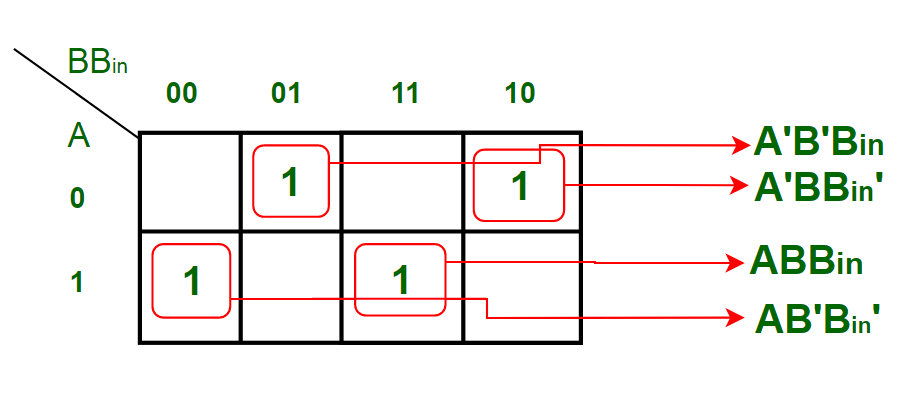

输出变量 ‘D’ 的 K-map 简化:

从上面的K-map得到的方程是,

D = A'B'Bin + AB'Bin' + ABBin + A'BBin'可以简化为,

D = B'(A'Bin + ABin') + B(ABin + A'Bin')

D = B'(A xor Bin) + B(A xor Bin)'

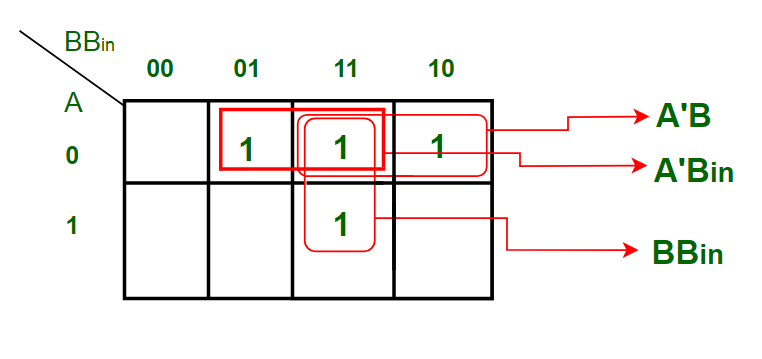

D = A xor B xor Bin 输出变量 ‘B out ‘ 的 K-map 简化:

得到的方程是,

Bout = BBin + A'B + A'Bin 全减法器逻辑图:

应用:

- 用于在电子计算器和其他数字设备中执行算术计算。

- 在定时器和程序计数器中。

- 在数字信号处理中很有用。