📌 相关文章

- 二进制加法器(1)

- 二进制加法器

- 加法器

- 加法器(1)

- COA |二进制增量器

- COA |二进制增量器(1)

- 半加法器和全加法器之间的区别

- 半加法器和全加法器之间的区别(1)

- COA |二进制加减法

- COA |二进制加减法(1)

- 串行加法器和并行加法器的区别

- 串行加法器和并行加法器的区别

- 串行加法器和并行加法器的区别

- 串行加法器和并行加法器的区别(1)

- COA |主内存(1)

- COA |主内存

- 数字逻辑中的串行二进制加法器

- 数字逻辑中的串行二进制加法器

- 数字逻辑中的串行二进制加法器(1)

- 完全加法器

- 实现半加法器的 C++ 程序(1)

- 实现半加法器的 C++ 程序

- coa 对 npm 有什么用 - Javascript (1)

- COA |寄存器(1)

- COA |寄存器

- coa 对 npm 有什么用 - Javascript 代码示例

- COA |编码器

- COA |编码器(1)

- coa 主题中的角度法 (1)

📜 COA |二进制加法器

📅 最后修改于: 2020-12-29 11:23:15 🧑 作者: Mango

二进制加法器

加微操作需要可以保存数据的寄存器和可以执行算术加法的数字组件。

二进制加法器是一种数字电路,可以对任意长度的两个二进制数进行算术求和。

二进制加法器是使用串联的全加法器电路构成的,一个全加法器的输出进位连接到下一个全加法器的输入进位。

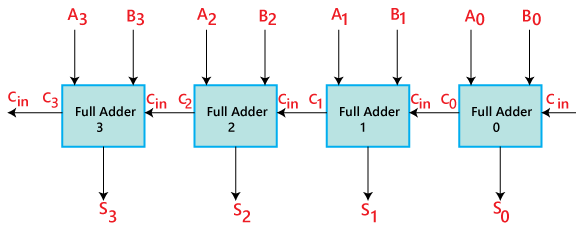

以下框图显示了四个全加法器电路的互连,以提供一个4位二进制加法器。

- 增数位(A)和加数位(B)由下标编号从右到左指定,下标'0'表示低位。

- 进位输入从C0到C3通过全加器成链连接。 C4是最后一个全加器电路产生的合成输出进位。

- 每个全加器的输出进位连接到下一个高阶全加器的输入进位。

- 和输出(S0至S3)生成所需的加数和加数位的算术和。

- A和B输入的n个数据位来自不同的源寄存器。例如, A输入的数据位来自源寄存器R1, B输入的数据位来自源寄存器R2。

- A和B的数据输入的算术和可以传输到第三寄存器或源寄存器之一(R1或R2)。