📌 相关文章

- 加法器

- 半加法器和全加法器之间的区别(1)

- 半加法器和全加法器之间的区别

- 二进制加法器(1)

- 二进制加法器

- 串行加法器和并行加法器的区别

- 串行加法器和并行加法器的区别

- 串行加法器和并行加法器的区别

- 串行加法器和并行加法器的区别(1)

- 实现半加法器的 C++ 程序(1)

- 实现半加法器的 C++ 程序

- COA |二进制加法器

- COA |二进制加法器(1)

- 十进制或BCD加法器

- 十进制或BCD加法器(1)

- 数字逻辑中的 BCD 加法器(1)

- 数字逻辑中的 BCD 加法器

- 数字逻辑中的 BCD 加法器

- 数字逻辑中的 BCD 加法器(1)

- 完全二叉树(1)

- 完全二叉树

- 如何完全删除php(1)

- 数字逻辑中的加法器和减法器(1)

- 数字逻辑中的加法器和减法器

- 数字逻辑中的加法器和减法器(1)

- 数字逻辑中的加法器和减法器

- 完全二叉树和完全二叉树的区别(1)

- 完全二叉树和完全二叉树的区别

- 从一个数组中打印所有完全数,其数字总和也是一个完全数

📜 完全加法器

📅 最后修改于: 2020-12-30 06:38:25 🧑 作者: Mango

完全加法器

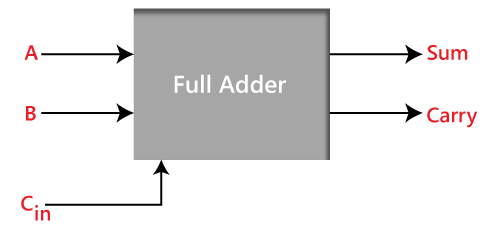

半加法器仅用于将两个数字相加。为了克服这个问题,开发了全加法器。全加法器用于将三个1位二进制数A,B和进位C相加。全加法器具有三个输入状态和两个输出状态,即和和进位。

框图

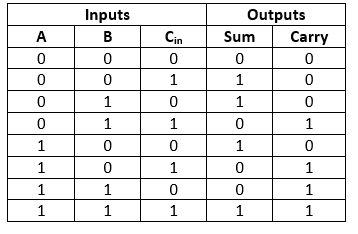

真相表

在上表中

- “ A”和“ B”是输入变量。这些变量代表将要添加的两个有效位

- “ C in ”是代表进位的第三个输入。从前一个较低的有效位置中,取出进位位。

- “ Sum”和“ Carry”是定义输出值的输出变量。

- 输入变量下的八行指定了这些变量中可能出现的0和1的所有可能组合。

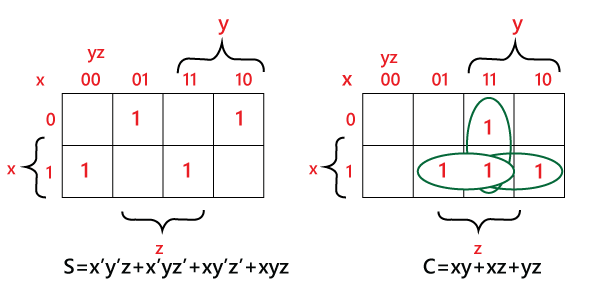

注意:我们可以借助独特的map方法简化每个输出“ Boolean 函数”。

可以借助K-map获得SOP表格,如下所示:

和= x'y'z + x'yz + xy'z'+ xyz

进位= +="" p="" xy="" xz="" yz<="">

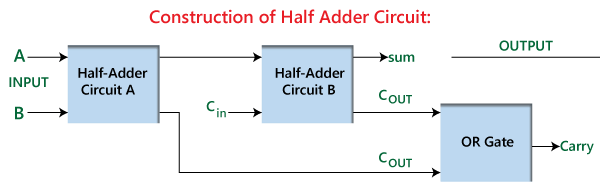

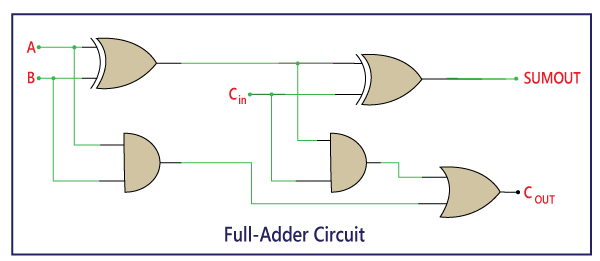

半加法器电路的构造:

上面的框图描述了全加法器电路的结构。在上面的电路中,有两个使用“或”门组合的半加法器电路。前半加法器有两个单位二进制输入A和B。众所周知,半加法器产生两个输出,即Sum和Carry。第一个加法器的“ Sum”输出将是第二个半加法器的第一个输入,第一个加法器的“ Carry”输出将是第二个半加法器的第二个输入。后半加法器将再次提供“ Sum”和“ Carry”。全加器电路的最终结果是“求和”位。为了找到“ Carry”的最终输出,我们将第一个和第二个加法器的“ Carry”输出提供给“或”门。或门的结果将是整个加法器电路的最终进位。

MSB由最后的“ Carry”位表示。

全加器逻辑电路可以使用“AND”和“被构造XOR”门用OR门。

上图显示了全加法器的实际逻辑电路。完整的加法器电路结构也可以用布尔表达式表示。

和:

- 对输入A和B执行XOR操作。

- 用进位执行结果的XOR操作。因此,总和为(A XOR B)XOR C ,其中也表示为:(A⊕B)⊕C in

携带:

- 执行输入A和B的“与”操作。

- 对输入A和B执行“ XOR”操作。

- 对来自前两个步骤的两个输出执行“或”运算。因此,“ Carry”可以表示为:AB +(A⊕B)