📌 相关文章

- 半加法器和全加法器之间的区别

- 半加法器和全加法器之间的区别(1)

- 二进制加法器(1)

- 二进制加法器

- 串行加法器和并行加法器的区别

- 串行加法器和并行加法器的区别

- 串行加法器和并行加法器的区别(1)

- 串行加法器和并行加法器的区别

- 完全加法器

- 实现半加法器的 C++ 程序(1)

- 实现半加法器的 C++ 程序

- COA |二进制加法器(1)

- COA |二进制加法器

- 十进制或BCD加法器(1)

- 十进制或BCD加法器

- 数字逻辑中的 BCD 加法器(1)

- 数字逻辑中的 BCD 加法器(1)

- 数字逻辑中的 BCD 加法器

- 数字逻辑中的 BCD 加法器

- 数字逻辑中的加法器和减法器

- 数字逻辑中的加法器和减法器(1)

- 数字逻辑中的加法器和减法器

- 数字逻辑中的加法器和减法器(1)

- 数字逻辑中的串行二进制加法器

- 数字逻辑中的串行二进制加法器(1)

- 数字逻辑中的串行二进制加法器

- 进位前瞻加法器

- 一半?加法器计算机组织和架构教程(1)

- 一半?加法器计算机组织和架构教程

📜 加法器

📅 最后修改于: 2020-12-30 06:37:31 🧑 作者: Mango

半加法器

Half-Adder是将两个数字相加为两个输入并产生两个输出的基本构建块。加法器用于对两个一位二进制数执行“或”运算。紧急和加法位是两个输入状态, “进位”和“求和”是半加法器的两个输出状态。

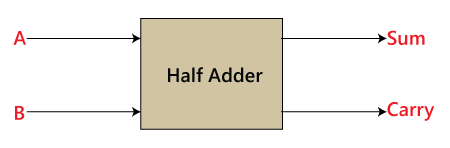

框图

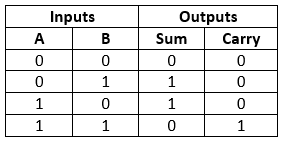

真相表

在上表中

- “ A”和“ B”是输入状态,“和”和“进位”是输出状态。

- 如果两个输入都不为1,则进位输出为0。

- 总和的最低有效位由“求和”位定义。

SOP形式的总和和如下:

总和= x'y + xy'

进位= p="" xy<="">

半加法器电路的构造:

在框图中,我们看到它包含两个输入和两个输出。紧急和加法位是输入状态,进位和总和是半加法器的输出状态。半加法器是在以下两个逻辑门的帮助下设计的:

- 2输入与门。

- 2输入异或门或异或门

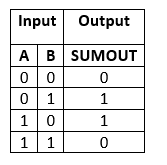

1. 2输入异或门或异或门

求和位与异或或者异或门的帮助下产生的。

以上是EX-OR门的符号。在上图中,“ A”和“ B”是输入,而“ SUMOUT”是对两个数字执行XOR运算后的最终结果。

EX-OR门的真值表如下:

从上表可以明显看出,当两个输入都不相同时, 请单击此处。

2. 2输入与门:

XOR门无法生成进位位。为此,我们使用另一个称为AND Gate的门。 AND门给出进位的正确结果。

以上是与门的符号。在上图中,“ A”和“ B”是输入,而“ OUT”是对两个数字进行“与”运算后的最终结果。

以下是AND门的真值表:

从上表中可以明显看出,当两个输入均为1时,与门给出的结果为1。当两个输入都不相同且为0时,与门给出的结果为0。要详细了解与门,请点击这里。

半加法逻辑电路:

因此,半加法器是通过组合“ XOR”和“ AND”门并提供总和和进位而设计的。

Half Adder电路具有以下布尔表达式:

总和= A XOR B(A + B)

进位= A和B(AB)

进位=>