- Verilog D闩锁

- Verilog D闩锁(1)

- Verilog数组(1)

- Verilog数组

- Verilog函数(1)

- Verilog函数

- Verilog模块

- Verilog模块(1)

- Verilog参数(1)

- Verilog参数

- Verilog运算符(1)

- Verilog运算符

- Verilog教程

- Verilog块语句

- Verilog块语句(1)

- Verilog端口

- Verilog端口(1)

- rtl bootstrap (1)

- bootstrap rtl (1)

- Verilog分配

- Verilog分配(1)

- Verilog数据类型

- Verilog 数据类型

- Verilog数据类型(1)

- Verilog 数据类型(1)

- Verilog控制块

- Verilog控制块(1)

- Verilog任务(1)

- Verilog任务

📅 最后修改于: 2021-01-11 14:38:07 🧑 作者: Mango

RTL Verilog

在数字电路设计中,寄存器传输级(RTL)是一种设计抽象,它根据硬件寄存器之间的数据流以及对这些信号执行的逻辑运算来对同步数字电路进行建模。

在HDL中使用寄存器传输级抽象来创建电路的高级表示,从中可以得出较低级别的表示,并最终得出实际的布线。 RTL级别的设计是现代数字设计中的典型实践。

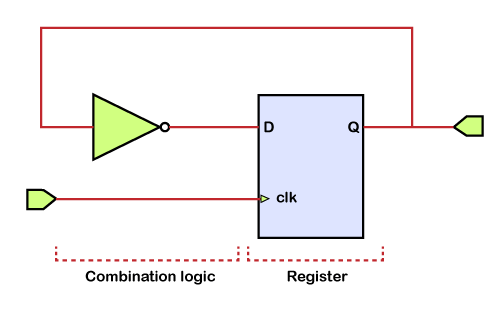

同步电路由两个元素组成,例如:

- 寄存器(顺序逻辑):寄存器将电路的操作同步到时钟信号的边沿,并且是电路中唯一具有存储器属性的元素。它们通常被实现为D型触发器。

- 组合逻辑:组合逻辑执行电路中的所有逻辑功能。它由逻辑门组成。

例如,下图显示了一个简单的同步电路。反相器从输出Q连接到寄存器的输入D,以创建电路。它在CLK的每个上升沿改变其状态。在该电路中,组合逻辑由逆变器组成。

在使用硬件描述语言设计数字集成电路时,通常以比晶体管级或逻辑门级更高的抽象级来安排设计。

在HDL中,设计人员声明寄存器,这些寄存器大致对应于编程语言中的变量,并使用诸如if-then-else和算术运算之类的结构描述组合逻辑。

此级别称为寄存器传输级别或RTL 。 RTL一词的重点是描述寄存器之间的信号流。

通常可以使用EDA工具将该描述直接转换为等效的硬件实现文件,以进行综合。综合工具还执行逻辑优化。

在寄存器传输级别,可以识别某些类型的电路。如果从寄存器的输出到其输入存在逻辑的循环路径,则该电路称为状态机或顺序逻辑。

如果存在从一个寄存器到另一个寄存器的逻辑路径而没有循环,则称为流水线。

RTL电路设计周期

RTL用于集成电路设计周期的逻辑设计阶段。通过逻辑综合工具将RTL描述转换为电路的门级描述。

然后,布局结果和布线工具将使用合成结果来创建物理布局。逻辑仿真工具可以使用设计的RTL描述来验证其正确性。

功率估算技术

最准确的功率分析工具可用于电路级,但是即使使用开关而不是设备级建模,电路级工具也有缺点。它们要么太慢,要么需要太多内存。

其中大多数是SPICE之类的仿真器,设计人员多年来一直将其用作性能分析工具。

由于这些缺点,门级功率估计工具已开始获得一定的认可,而更快的概率技术已开始立足。

但是,由于要以提高精度为代价(尤其是在存在相关信号的情况下)才能实现加速,因此也需要权衡。

多年来,人们已经认识到低功耗设计不能来自电路和门级优化。相反,系统,体系结构和算法优化往往会对功耗产生最大的影响。因此,工具开发人员已经倾向于使用高级的电源分析和优化工具。

门等效技术

这是一种基于门等效概念的技术。芯片架构的复杂性可以大致按照门等效项来描述,其中等效门数指定实现特定函数所需的参考门的平均数量。

通过将近似的栅极等效值乘以每个栅极消耗的平均功率,可以估算出特定函数所需的总功率。参考门可以是任何门,例如2输入与非门。该技术以以下类型分布,例如:

1.类无关的功率建模:这是一种技术,它试图根据有关门极等效性的设计复杂性信息来估计芯片面积,速度和功耗。

功能被划分在不同的块之间,但是在这些块的功能上没有区别。

它是与类无关的。芯片估计系统(CES)使用此技术。此技术完成以下步骤:

步骤1:确定功能块,例如计数器,解码器,乘法器,存储器等。

步骤2:根据门等效值分配复杂度。每种单位类型的GE的数量可以直接作为用户输入,也可以从库中获取。

2.类依赖功率建模:这种方法比以前的方法稍好,因为它考虑了针对不同类型功能块的定制估计技术。

因此,它试图提高建模精度,而在诸如逻辑,内存,互连和时钟之类的先前技术中则没有。

功率估计以与独立情况非常相似的方式进行。基本开关能量基于三输入与门,并根据用户提供的技术参数(例如门宽度,毒物和金属宽度)计算得出。

缺点

这种方法还具有以下缺点,例如:

- 由于假设整个芯片的总体活动因子,因此无法准确地对电路活动进行建模,因为用户提供的活动因子也不可信。

- 活性因子在整个芯片中会有所不同;因此,这不是很准确,并且容易出错。这导致了一个问题,即使模型给出了芯片总功耗的正确估计值,模块方向的功率分配也相对不准确。

- 选择的活动因子给出正确的总功率,但是将功率分解为逻辑,时钟,存储器等的准确性较低。

- 与CES相比,此工具没有太大不同或有所改进。

预表征细胞图书馆技术

该技术通过具有用于逻辑,存储器和互连的独立功率模型,进一步定制了各种功能块的功率估计。这些提出了一种功率因数逼近(PFA)方法,用于分别表征整个功能块库(例如乘法器,加法器等),而不是“逻辑”块的单个门等效模型。

优点

预表征的细胞库技术具有以下优点:

- 可以根据适合该块的任何复杂性参数进行定制。对于乘法器,字长的平方是合适的。

- 存储容量以位为单位用于内存,仅字长足以满足I / O驱动程序的需求。