- Verilog D闩锁(1)

- Verilog D闩锁

- Verilog数组

- Verilog数组(1)

- Verilog函数

- Verilog函数(1)

- Verilog模块

- Verilog模块(1)

- Verilog参数

- Verilog参数(1)

- Verilog运算符

- Verilog运算符(1)

- Verilog教程

- Verilog块语句

- Verilog块语句(1)

- Verilog端口

- Verilog端口(1)

- Verilog分配(1)

- Verilog分配

- Verilog数据类型

- Verilog 数据类型(1)

- Verilog 数据类型

- Verilog数据类型(1)

- Verilog控制块

- Verilog控制块(1)

- Verilog任务

- Verilog任务(1)

- Verilog文件操作

- Verilog文件操作(1)

📅 最后修改于: 2021-01-11 14:44:49 🧑 作者: Mango

Verilog初始块

Always块指示自由运行的进程,而初始块指示一个进程仅执行一次。这两个构造都在模拟器时间0开始执行,并且都执行到块结束。

初始块可以用于可合成块或不可合成块。它们通常用于测试台。

初始块会导致在仿真开始之前执行其他特定指令,然后再执行其他任何指令。初始块只能运行一次。

可综合的初始块用于设置FPGAROM的上电值。但是,初始块不能在ASIC或CPLD中合成。

起始块和始终块描述了独立的流程,这意味着一个流程中的语句将自动执行。

两种类型的过程都由过程语句组成,并且都在模拟器启动时立即启动。

它们之间的主要区别是:

- 初始进程执行一次,而始终进程则永远重复执行。

- Always进程必须包含时序语句,这些语句有时会阻止执行并留出时间。

句法

Verilog初始块遵循以下语法:

initial

[single statement]

initial begin

[multiple statements]

end

初始块用途

初始块不可合成,无法将其转换为带有数字元素的硬件原理图。

初始块没有比在仿真中使用更多的目的。这些块主要用于初始化变量和驱动具有特定值的设计端口。

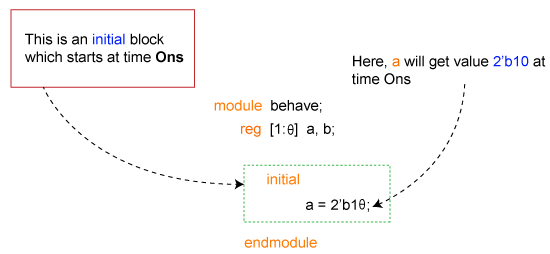

初始块执行

在仿真开始时以时间0单位开始一个初始块。在整个模拟过程中,该块仅执行一次。一旦执行了块中的所有语句,就完成了初始块的执行,如下图所示。

上面显示的图像有一个称为行为的模块,该模块具有a和b内部信号。

初始块只有一个语句,因此没有必要将语句放在开始和结束之间。

当初始块以时间0单位开始时,该语句将值2'b10分配给a。

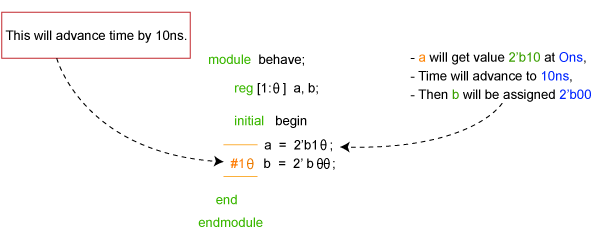

初始块延迟元素

下面显示的代码还有一个附加的语句,该语句为信号b分配一些值。但是,仅在执行上一条语句10次后才发生这种情况。

例如,如果首先为a分配给定值,然后以10倍为单位,则b分配为0。

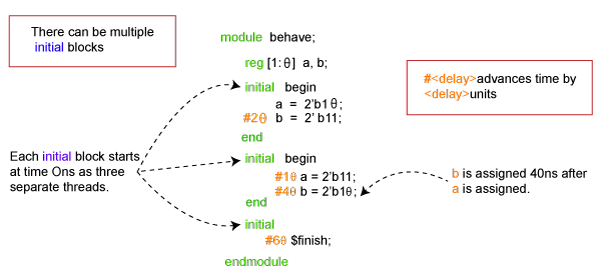

模块中的初始块

对模块内部可以定义的初始块的数量没有限制。下面显示的代码具有三个初始块,所有这些块同时启动并并行运行。

但是,根据每个初始块中的语句和延迟,完成该块所花费的时间可能会有所不同。

注意:$ finish是一个Verilog系统任务,它告诉模拟器终止当前模拟。

在上图中,第一个块的延迟为20个单位,而第二个块的总延迟为50个单位(10 + 40),最后一个块的延迟为60个单位。因此,由于至少有一个初始块仍在运行直到60个时间单位,因此仿真需要60个时间单位才能完成。

如果最后一个块具有30个时间单位的延迟,如下所示,则模拟将以30个时间单位结束,从而杀死当时所有处于活动状态的其他初始块。

initial begin

#30 $finish;

end