- Verilog D闩锁

- Verilog数组(1)

- Verilog数组

- Verilog函数(1)

- Verilog函数

- Verilog模块

- Verilog模块(1)

- Verilog参数

- Verilog参数(1)

- Verilog内部和内部延迟

- Verilog内部和内部延迟(1)

- Verilog运算符

- Verilog运算符(1)

- Verilog教程

- Verilog块语句

- Verilog块语句(1)

- javascript中的延迟(1)

- Verilog端口(1)

- Verilog端口

- Verilog分配

- Verilog分配(1)

- Verilog 数据类型

- Verilog 数据类型(1)

- Verilog数据类型(1)

- Verilog数据类型

- php中的延迟(1)

- Verilog控制块

- Verilog控制块(1)

- Verilog任务

📅 最后修改于: 2021-01-11 14:55:35 🧑 作者: Mango

Verilog门延迟

Verilog门延迟指定值如何通过网络或门传播。门延迟声明指定了将信号变化从门输入传播到其输出所需的时间。

门延迟声明可用于门实例化。延迟还可以用于过程语句中的延迟控制。

数字元件是二进制实体,并且仅保存两个值0和1。从0到1和1到0的转换具有转换延迟,因此每个门元件都将值从输入传播到其输出。

例如,如果两个输入均变为1,则两个输入与门必须将输出切换为1,而当输入变为0时,则必须将其切换回0。

网络延迟声明指定了通过网络从驱动程序传播值所需的时间。它可以用于连续分配和净声明。

实例化逻辑原语时,可以在Verilog中指定此门和引脚到引脚的延迟。

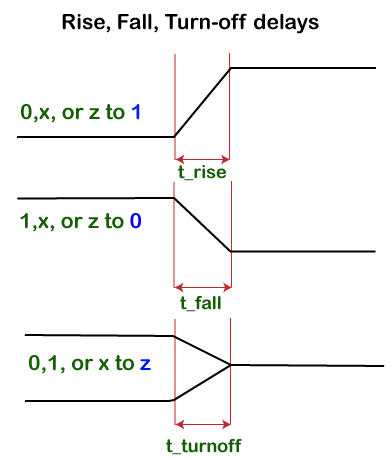

上升,下降和关闭延迟

延迟声明最多可以包含三个值,例如上升,下降和关闭延迟。

- 门输出从某个值变为1所需的时间称为上升延迟。

- 门的输出从某个值变为0所需的时间称为下降延迟。

- 栅极输出从某个值变为高阻抗所需的时间称为关闭延迟。

如果仅指定一个延迟值,则将其用于所有信号更改。默认延迟为零。

如果指定了两个延迟,则第一个延迟指定上升延迟,第二个延迟指定下降延迟。

如果信号变为高阻抗或未知,则将使用较小的值。

如果给出三个值,则第一个值指定上升延迟,第二个值指定下降延迟,第三个值指定关断延迟。如果信号变为未知值,则将使用这三个值中的最小值。

这些延迟适用于任何信号,因为它们在实际电路中随时都可能上升或下降,并且不仅限于门的输出。有三种表示门延迟的方法。

- 一种延迟格式

- 两种延迟格式

- 三延迟格式

两种延迟格式可以应用于其输出不会转变为高阻抗的大多数图元。

三延迟格式不能应用于AND门,因为任何输入组合的输出都不会变为Z。

// Single delay specified - used for all three types of transition delays

or #() o1 (out, a, b);

// Two delays specified - used for Rise and Fall transitions

or #(, ) o1 (out, a, b);

// Three delays specified - used for Rise, Fall and Turn-off transitions

or #(, , ) o1 (out, a, b);

如果仅指定一个延迟,则所有三种类型的延迟将使用相同的给定值。

如果指定了两个延迟,则第一个代表上升,第二个代表下降。

如果指定了三个延迟,则它们分别代表上升,下降和关闭延迟。

1.一种延迟格式

module des (input a, b, output out1, out2);

// AND gate has 2 time unit gate delay

and #(2) o1 (out1, a, b);

// BUFIF0 gate has 3 time unit gate delay

bufif0 #(3) b1 (out2, a, b);

endmodule

现在,看到“与”门的输出在其输入之一改变后改变2个时间单位。

module tb;

reg a, b;

wire out1, out2;

des d0 (.out1(out1), .out2(out2), .a(a), .b(b));

initial begin

{a, b} <= 0;

$monitor ("T=%0t a=%0b b=%0b and=%0b bufif0=%0b", $time, a, b, out1, out2);

#10 a <= 1;

#10 b <= 1;

#10 a <= 0;

#10 b <= 0;

end

endmodule

例如,在T = 20时b变为1,而a已经为1。但是,仅在T = 22时输出变为1。同样,a在T = 30时回到零,并且输出在T = 32时获得新值。

门延迟指定为BUFIF0的3时间单位。如果b从0变为1,而a已经为1,则输出以3倍为单位更新为Z,最后在T = 23进行更新。

输出量

ncsim> run

T=0 a=0 b=0 and=x bufif0=x

T=2 a=0 b=0 and=0 bufif0=x

T=3 a=0 b=0 and=0 bufif0=0

T=10 a=1 b=0 and=0 bufif0=0

T=13 a=1 b=0 and=0 bufif0=1

T=20 a=1 b=1 and=0 bufif0=1

T=22 a=1 b=1 and=1 bufif0=1

T=23 a=1 b=1 and=1 bufif0=z

T=30 a=0 b=1 and=1 bufif0=z

T=32 a=0 b=1 and=0 bufif0=z

T=40 a=0 b=0 and=0 bufif0=z

T=43 a=0 b=0 and=0 bufif0=0

ncsim: *W,RNQUIE: Simulation is complete.

2.两种延迟格式

让我们将上面显示的相同测试平台应用于下面显示的不同Verilog模型,其中明确提到了上升和下降延迟。

module des (input a, b, output out1, out2);

and #(2, 3) o1 (out1, a, b);

bufif0 #(4, 5) b1 (out2, a, b);

endmodule

并产生以下输出,例如:

ncsim> run

T=0 a=0 b=0 and=x bufif0=x

T=3 a=0 b=0 and=0 bufif0=x

T=5 a=0 b=0 and=0 bufif0=0

T=10 a=1 b=0 and=0 bufif0=0

T=14 a=1 b=0 and=0 bufif0=1

T=20 a=1 b=1 and=0 bufif0=1

T=22 a=1 b=1 and=1 bufif0=1

T=24 a=1 b=1 and=1 bufif0=z

T=30 a=0 b=1 and=1 bufif0=z

T=33 a=0 b=1 and=0 bufif0=z

T=40 a=0 b=0 and=0 bufif0=z

T=45 a=0 b=0 and=0 bufif0=0

ncsim: *W,RNQUIE: Simulation is complete.

3.三种延迟格式

module des ( input a, b, output out1, out2);

and #(2, 3) o1 (out1, a, b);

bufif0 #(5, 6, 7) b1 (out2, a, b);

endmodule

三种延迟格式代码提供以下输出:

ncsim> run

T=0 a=0 b=0 and=x bufif0=x

T=3 a=0 b=0 and=0 bufif0=x

T=6 a=0 b=0 and=0 bufif0=0

T=10 a=1 b=0 and=0 bufif0=0

T=15 a=1 b=0 and=0 bufif0=1

T=20 a=1 b=1 and=0 bufif0=1

T=22 a=1 b=1 and=1 bufif0=1

T=27 a=1 b=1 and=1 bufif0=z

T=30 a=0 b=1 and=1 bufif0=z

T=33 a=0 b=1 and=0 bufif0=z

T=40 a=0 b=0 and=0 bufif0=z

T=46 a=0 b=0 and=0 bufif0=0

ncsim: *W,RNQUIE: Simulation is complete.

最小,典型和最大延迟

在所制造芯片的不同部分中的延迟既不相同,对于不同温度和其他变化的延迟也不相同。因此,Verilog还为上述每种延迟类型提供了额外的控制级别。

每个数字栅极和晶体管单元都有基于过程节点指定的最小,典型和最大延迟,通常由制造厂的库提供。

对于上升,下降和关闭延迟,可以指定最小值,典型值和最大值这三个值,分别代表最小,典型和最大延迟。

这是Verilog中另一个延迟控制级别。在整个模拟运行中,只能使用“最小值”,“典型值”和“最大值”之一。

它是在仿真开始时指定的,并取决于所使用的仿真器。典型值是默认值。

min值是栅极被预期具有最低延迟值。

典型值是期望门具有的典型延迟值。

最大值是期望门具有的最大延迟值。

module des (input a, b, output out1, out2);

and #(2:3:4, 3:4:5) o1 (out1, a, b);

bufif0 #(5:6:7, 6:7:8, 7:8:9) b1 (out2, a, b);

endmodule

输出如下:

ncsim> run

T=0 a=0 b=0 and=x bufif0=x

T=4 a=0 b=0 and=0 bufif0=x

T=7 a=0 b=0 and=0 bufif0=0

T=10 a=1 b=0 and=0 bufif0=0

T=16 a=1 b=0 and=0 bufif0=1

T=20 a=1 b=1 and=0 bufif0=1

T=23 a=1 b=1 and=1 bufif0=1

T=28 a=1 b=1 and=1 bufif0=z

T=30 a=0 b=1 and=1 bufif0=z

T=34 a=0 b=1 and=0 bufif0=z

T=40 a=0 b=0 and=0 bufif0=z

T=47 a=0 b=0 and=0 bufif0=0

ncsim: *W,RNQUIE: Simulation is complete.